一、单片机简介

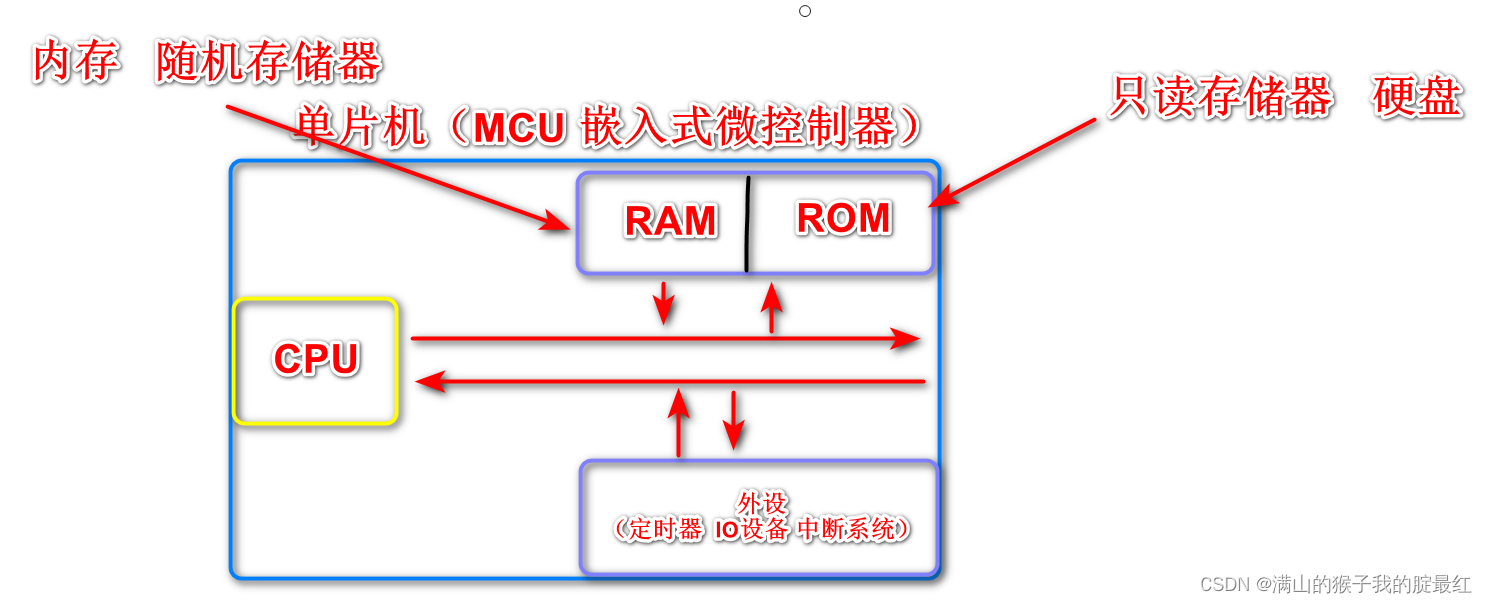

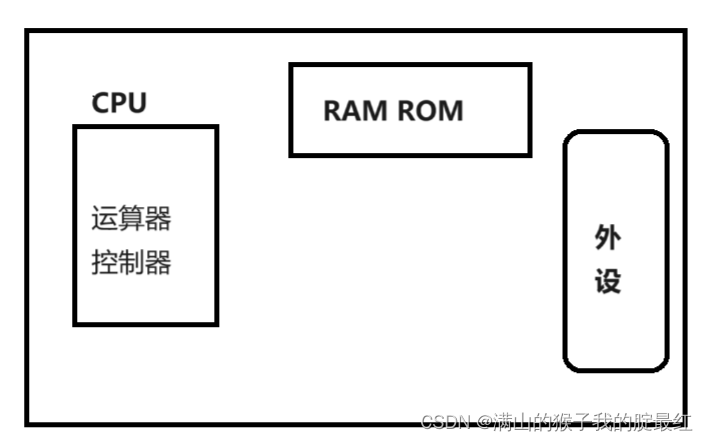

单片机是单片微型计算机的简称,MCU是Microcontroller的简称,也就是嵌入式微控制器。采用集成电路技术将具有数据处理能力的中央处理器CPU、随机存储器RAM、只读存储器ROM、定时器/计时器、多种I/O口和中断系统等功能集成到一块硅片上。可以说单片机就是一个小而完善的微型计算机系统。

SoC(System on Chip),片上系统SoC的定义多种多样,由于其内涵丰富、应用范围广,很难给出准确定义。一般说来, SoC称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。SoC就是定制功能版本的MCU

二、单片机型号

51单片机(8位)

STC89C51 宏晶科技 STC AT89C51 ATMEL

宏晶科技公司宏晶科技_百度百科

ATMEL公司

TI公司(16位)

MSP430

32单片机(32位)

STM32 意法半导体ST GD32 兆易创新GD

32位处理器:处理数据宽度是32位

处理器位数:CPU单次运算最大处理的数据位数

意法半导体

兆易创新

- 硬件基础

嵌入式工程师的硬件要学到什么程度呢?

嵌入式软件开发,本质上不需要你硬件非常精通,你可以不会画电路图,可以不会焊接,可以不会打PCB板。但是你需要懂电路基本原理,认识常用的元器件,能看懂电路图,会调试电路。尤其是越底层的开发(单片机、Linux驱动等)越接近硬件。当然,如果你能精通硬件更好,那你就是真正意义的嵌入式全栈工程师,这个需要看个人了,每个人精力都有限,软硬兼通需要很强的天赋及努力,而且要看工作后的机遇。有句话叫好的硬件工程师都是钱喂出来的,因为它的试错成本要远远高于软件。

1、 电路基础

电的类比

一般我们把电子知识想复杂了,实际电就可以理解为是水,电的特性和水的特性是类似的,因为电是看不见的,所以我们理解起来有困难。

电可以认为是看不见的水 电流类似于水流 电压类似于水压

电流

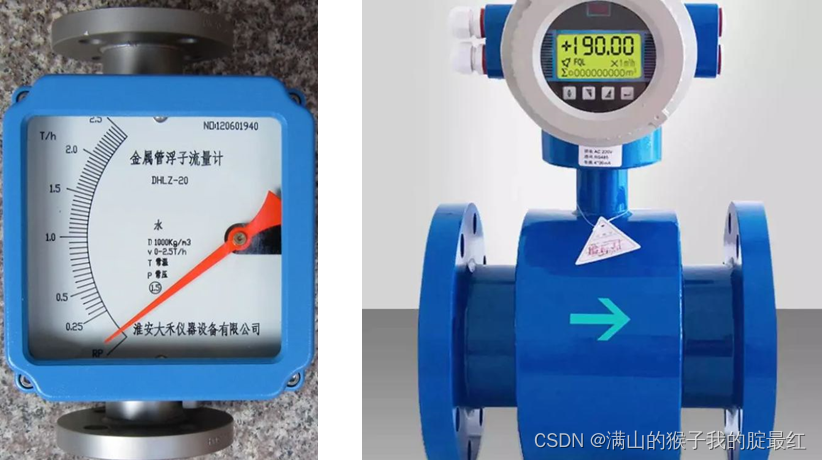

水流量计( 1单位流量= 1吨/小时=1T/H)

电流表(安培 1A= 1库伦/秒)

电流表实际就可以看成是水流表,就是计算水的流量,电的流量的意思。我们水管中流出了多少水,很容易理解,实际电在电线中流动,可以看成水的流动是一样的 。

电压

水压表 电压表

我们可以认为水压表测量水对水管的压力,电压表是测量电对电线的压力。水是从水压高的地方流到水压低的地方,电也是从电压高的地方流到电压低的地方。

电路

水到处流动 形成小河、小溪之类。电到处流动,形成什么,就是电路。水走的路是水路,电路这样就好理解了。

类比电路图

2、电子元器件

电路图中有很多元件,我们可以把很多元件看成水路中的很多元件就容易理解。

电阻

电阻实际是大小不同的水管让水流的小一点,慢一点,这样后面的器件,不至于受到大电流冲击搞坏了 。电阻无方向,电阻就是阻碍电的流动,你可以想象一个水管里有水垢,水垢越多,水阻越大,水流越小。同理,电阻越大,导体对电流的阻碍作用越大,电流越小。

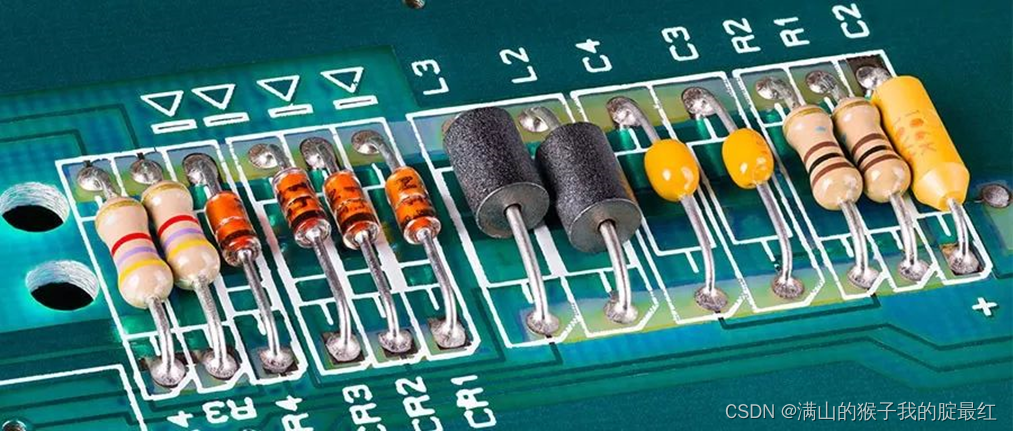

实物图

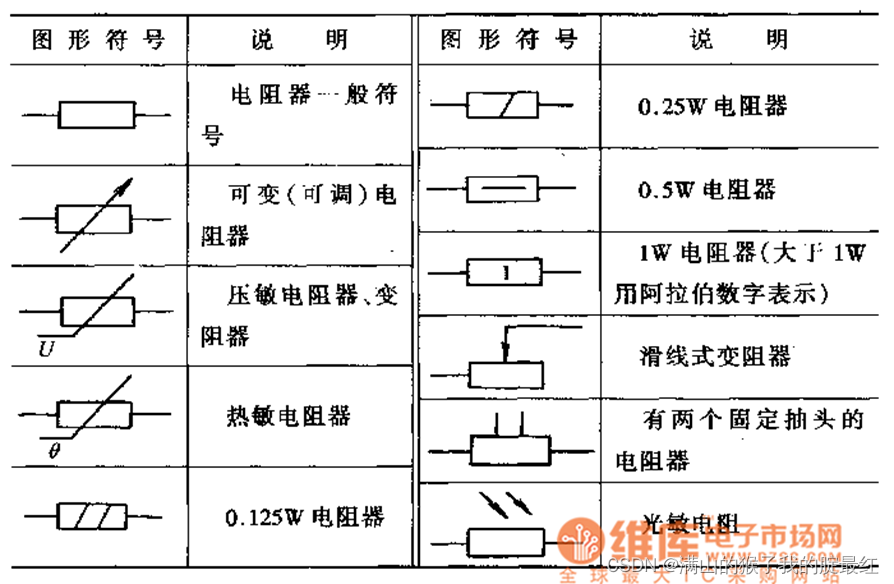

电路符号

电容

电容是可以理解成一个装水的容器(水桶、池塘、湖泊、水库),水要通过池塘、湖泊,首先需要灌满它才能过得去。所以这部分水(电能)可以被这些容器保存下来,这是电容的储能作用,另外很明显,无论前面的水流多么湍急,到了湖泊就要先灌满它,湖泊开口再向下游流水,自然流水就缓慢一些,所以它也有缓冲的作用。大波浪到了湖泊变平稳,实际变成了小波浪,波的形状都变了,这就是过滤的作用,只允许特定的波通过。

所以电容在电路中是储能、缓冲、减压、过滤器件。

同一颗电容在电路中摆放的位置不同,作用不同,也就是在这个电路中它主要起漏斗的作用,但是在另外的电路中,它就是做储能了。因为后面的元件需要是稳定的水流, 你可以这样想象我们拿着水桶往水缸里倒水的时候,水面上起的水花是很大的,这样的水花,对后面的器件是有损伤的。

实物

电路符号

电感

来拒去留

二极管

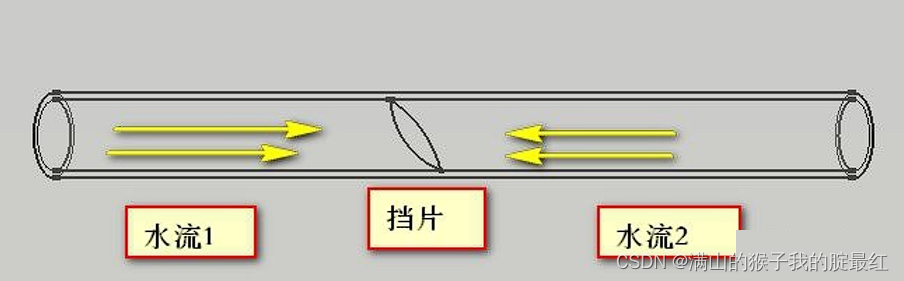

二极管实际是单向阀门, 意思就是说 水只能从一头进另一头出 。二极管就是这么个作用,它只能从一边过来的电能通过,从另一边过来的实际就过不去,记得电看成是水。

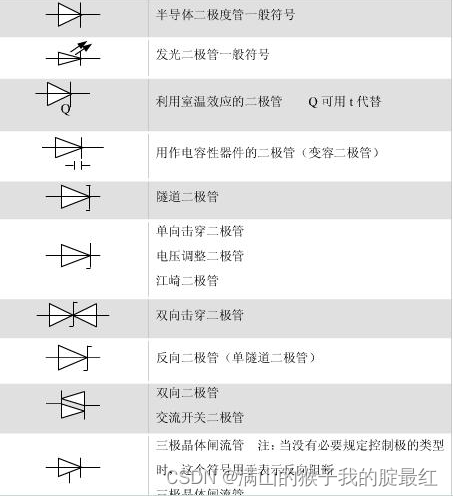

这个就是二极管的符号,很形象,右边有个竖杠,很明显,从左边来的电能流到右边,从右边来的就被挡到了。左边来挡片冲开,右边来抵死。

二极管在电路中的特性与水路中的单向阀基本原理一致。

实物

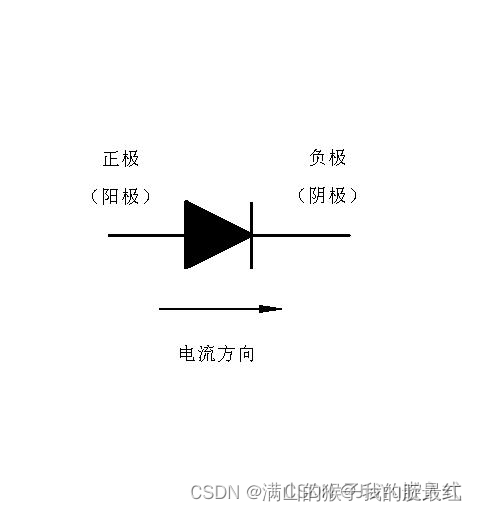

电路符号

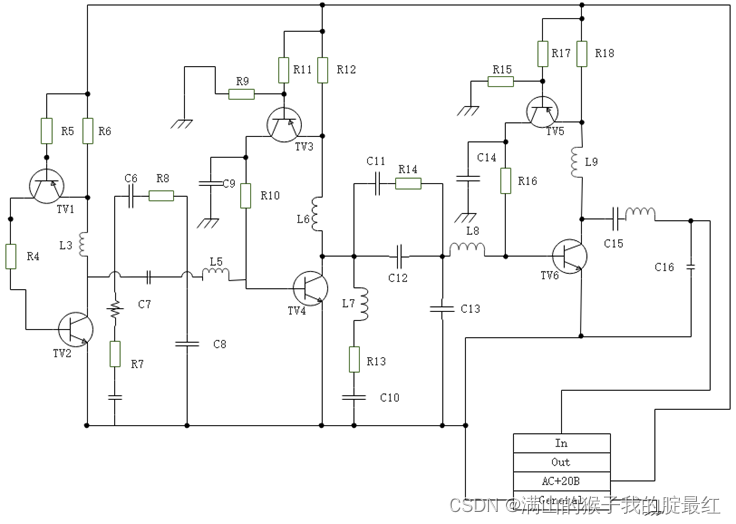

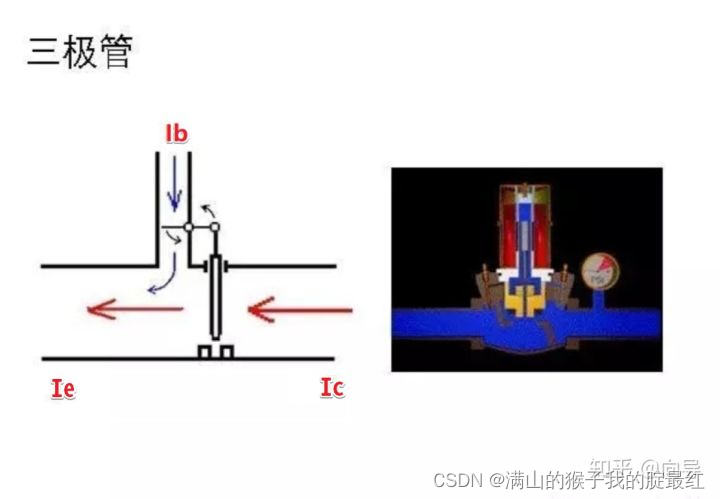

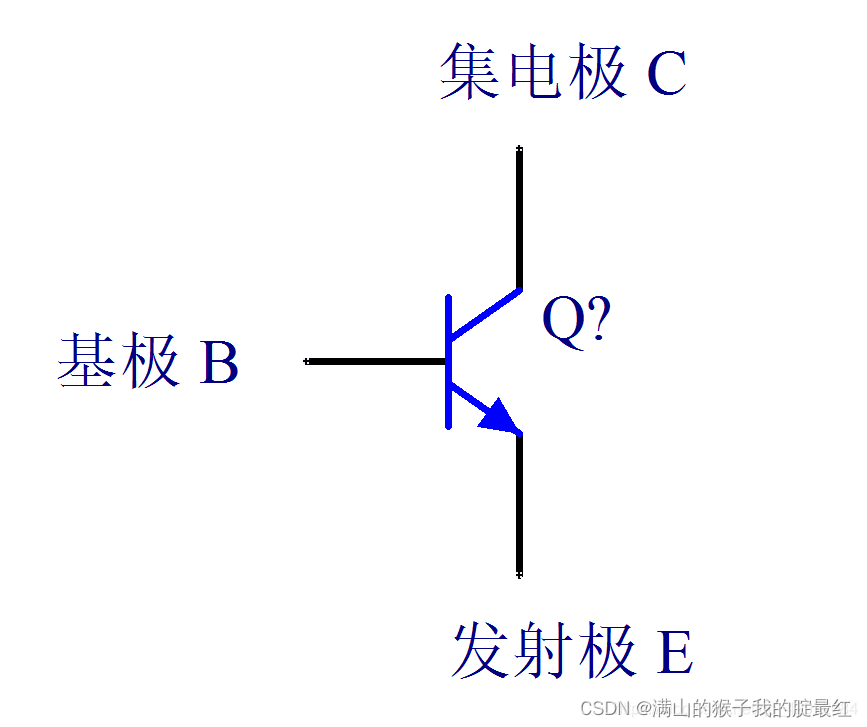

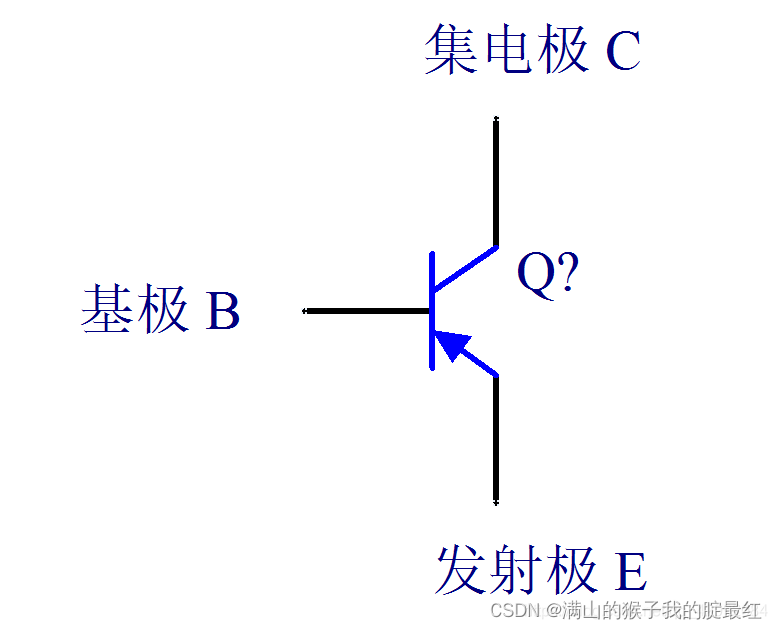

三极管

三极管实际是个小阀门控制大阀门的器件。(放大器)

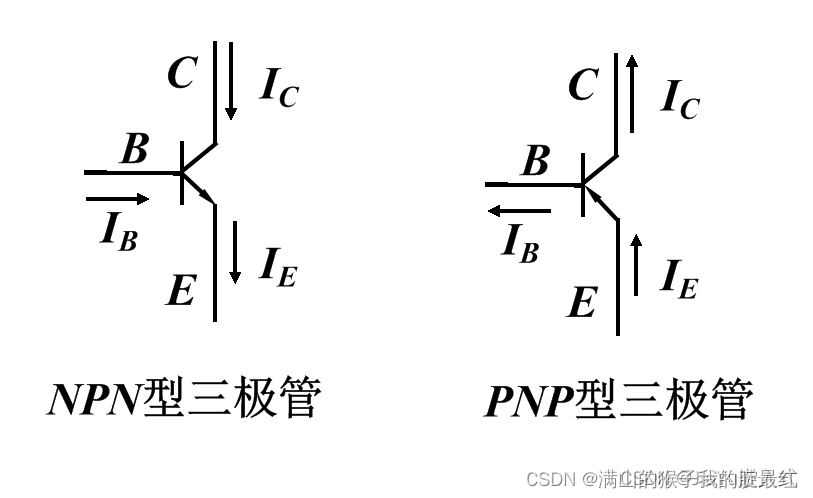

三极管有两种类型,PNP和NPN型。两者的不同参考:PNP9和NPN对比

终于有人讲了,凭什么三极管能放大?_哔哩哔哩_bilibili

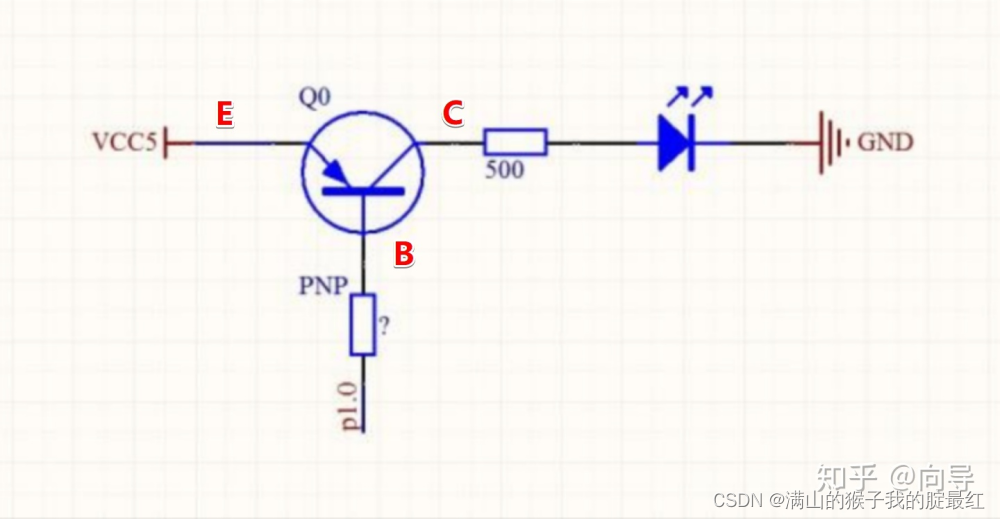

两种三极管使用时候决定着电路图的接法不同

如下是个常见的共基极PNP型电源控制开关

实物

电路符号

半导体三极管有三个电极:分别是基极、集电极和发射极。半导体管在工作时要加工作电压,于是就产生了各极电流。半导体三极管在工作时发射极电流等于基极和集电极电流之和。其中基极电流最小,发射极电流最大。在基极加一很小的电流,在集电极就能输出很大的电流,因此三极管有放大作用。三极管主要作用是放大信号。常用在放大电路和振荡电路中。

NPN:高通低断

PNP:低通高断

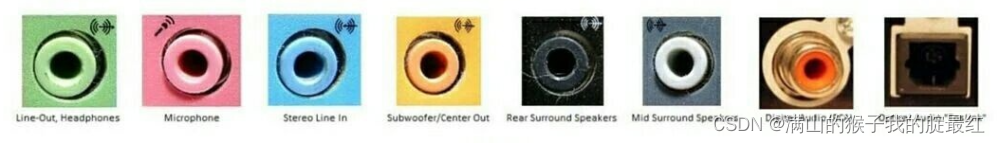

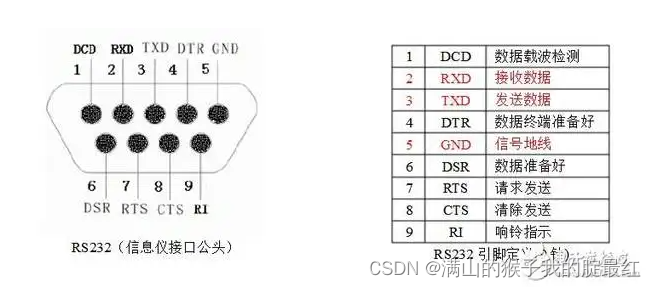

3 、常见电气接口

音频

视频

电源

RJ45网口

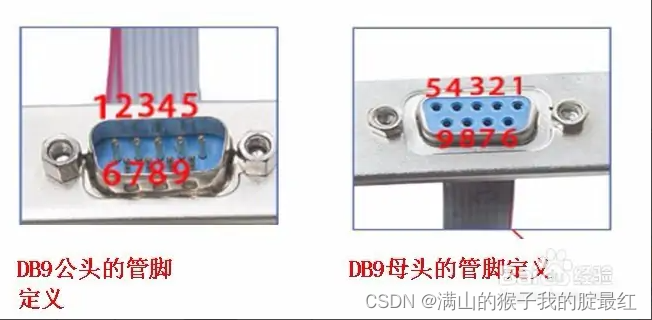

DB9串口

公头和母头

公头就是插头上是针的,母头就是插头上是孔的

线序及作用

实际开发过程中,线序可以去网上搜,只需要知道线序如何看,及红色的三条线即可。

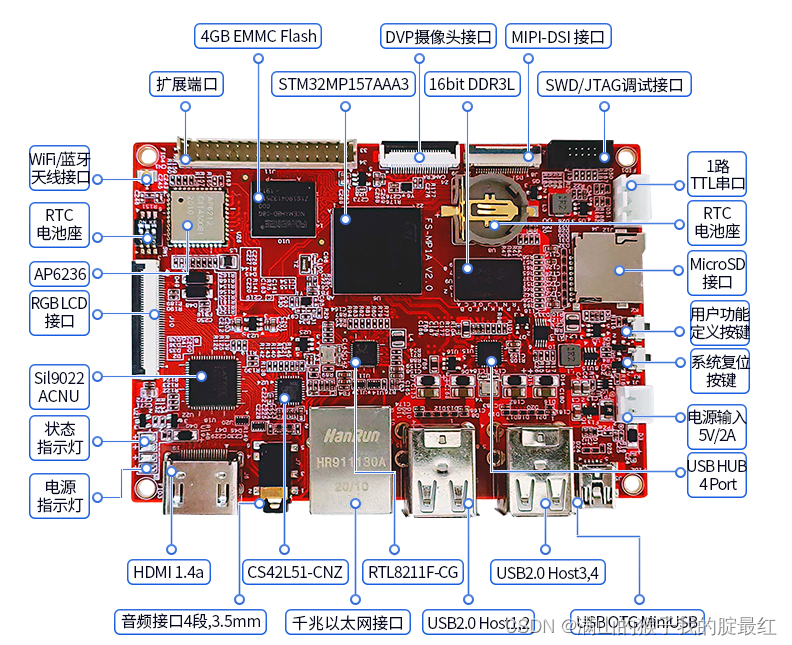

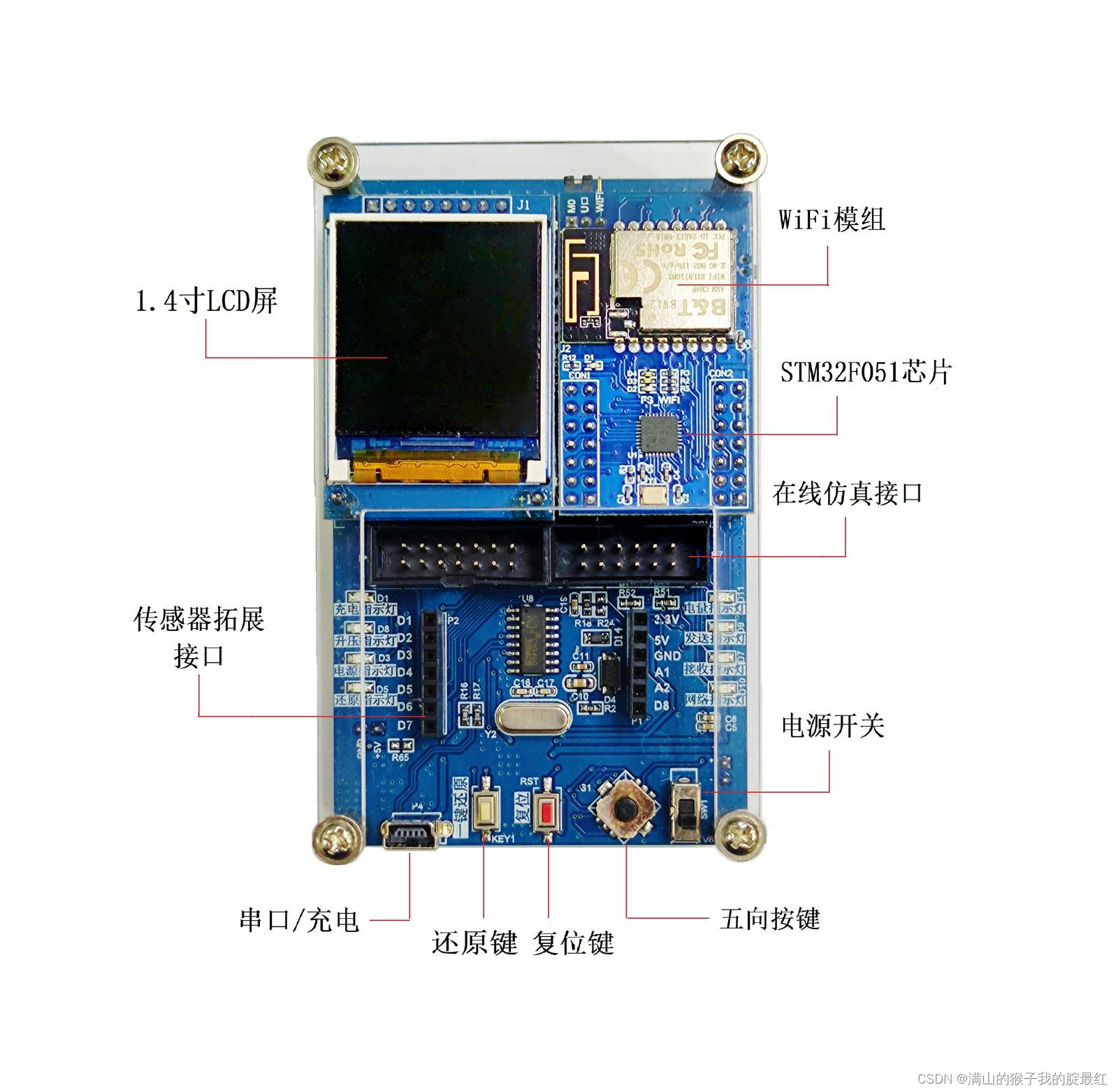

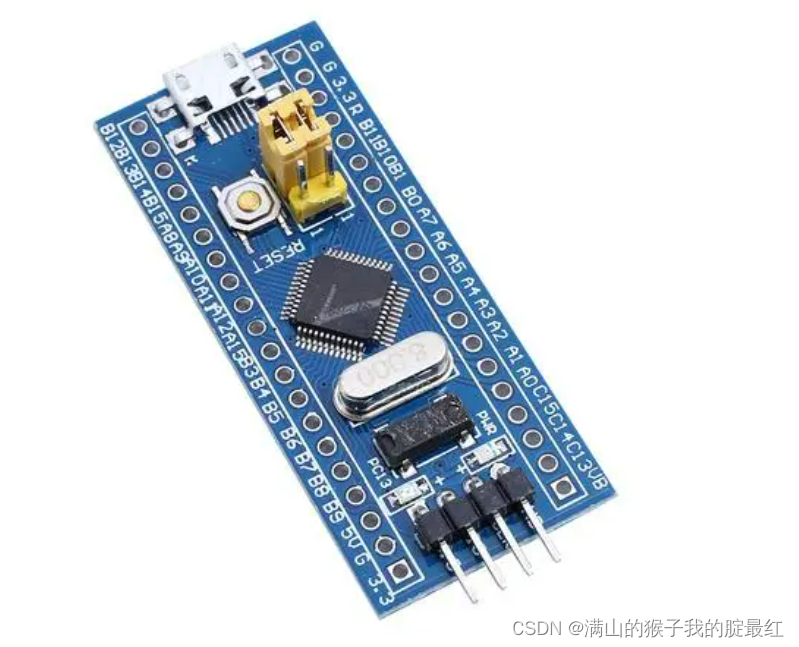

4、 开发板/最小系统板

开发板通常是学习用途,功能比较全,接口丰富,是用于研发、研究、学习的一块板子。

最小系统板是个核心板,集成了核心的通用功能,可以根据需求定制各种不同的底板,通用性较好。再者核心板作为一块独立的模块被分离出来,也降低了开发的难度,增加了系统的稳定性和可维护性通常用于做项目,也可以作为模块在产品里在直接用。

补充

PCB板(Printed Circuit Board),中文名称为印制电路板,又称印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气相互连接的载体。由于它是采用电子印刷术制作的,故被称为印刷电路板。印制电路板的设计是以电路原理图为根据,实现电路设计者所需要的功能。印刷电路板的设计主要指版图设计,需要考虑外部连接的布局。内部电子元件的优化布局、金属连线和通孔的优化布局、电磁保护、热耗散等各种因素。优秀的版图设计可以节约生产成本,达到良好的电路性能和散热性能。简单的版图设计可以用手工实现,复杂的版图设计需要借助计算机辅助设计(CAD)实现。

5、IO逻辑

计算机系统中的高低电平逻辑1和0,数据在计算机中的存储、传输、运算都是以二进制形式进行的。

计算机传输数据的方式只能使用电信号的方式表示二进制数据。

单片机: 高低电平 高电平 1 低电平0

0001 0010 0011

电压:电压差 电势差

模拟信号:模拟信号是连续的,模拟信号可以是任意数值状态;

数字信号:数字信号是离散(不连续)的,数字信号只有“0”和“1”两种状态

四、计算机知识铺垫

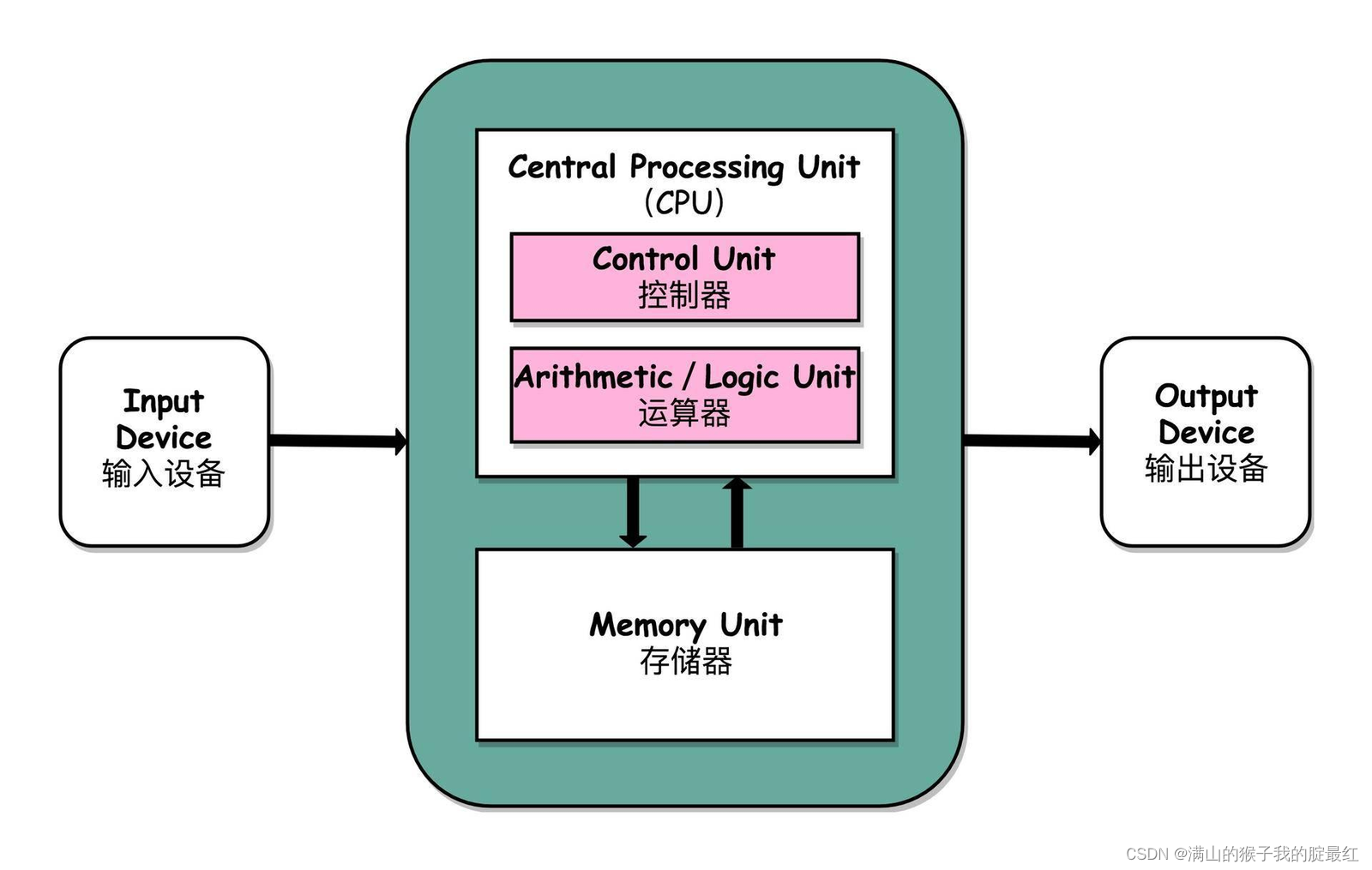

计算机的组成

输入设备、输出设备、存储器、运算器、控制器

1)输入设备:输入设备的任务是把人们编好的程序和原始数据送到计算机中去,并且把他们转换成计算机内部能够识别和接受的信息方式(鼠标、键盘、摄像头、麦克风、手柄)

2)输出设备:输出设备的任务是将计算器的处理结果以人或其他设备所能接受的形式送出去(音箱、屏幕)

3)存储器:用来存放程序和数据的部件,也是计算器能够实现存储功能。(硬盘、U盘、光盘、软盘、SD卡、TF卡、磁带、游戏卡带)

4)运算器:算术运算、逻辑运算

5)控制器:如从存储器中取出指令,控制计算机各部分协调运行

控制器和运算器整合在CPU中

单片机(MCU)的组成:

语言

机器码(不算语言):读写难(不可移植)

汇编:.s 可以读写(不能移植)

C语言:面向过程(可以和硬件打交道)

C++:即面向过程有面向对象(Qt(GUI)开发)

python、GO:爬虫类、客户端、数据分析、数据挖掘

C#:后端 上位机

易语言:

gcc编译流程四个步骤:

- 预处理:展开头文件(库)、进行宏替换

- 编译:检查代码的规范性、语法错误,没有错误会将代码编译成汇编语言

- 汇编:转换成二进制目标文件

- 链接:可执行文件

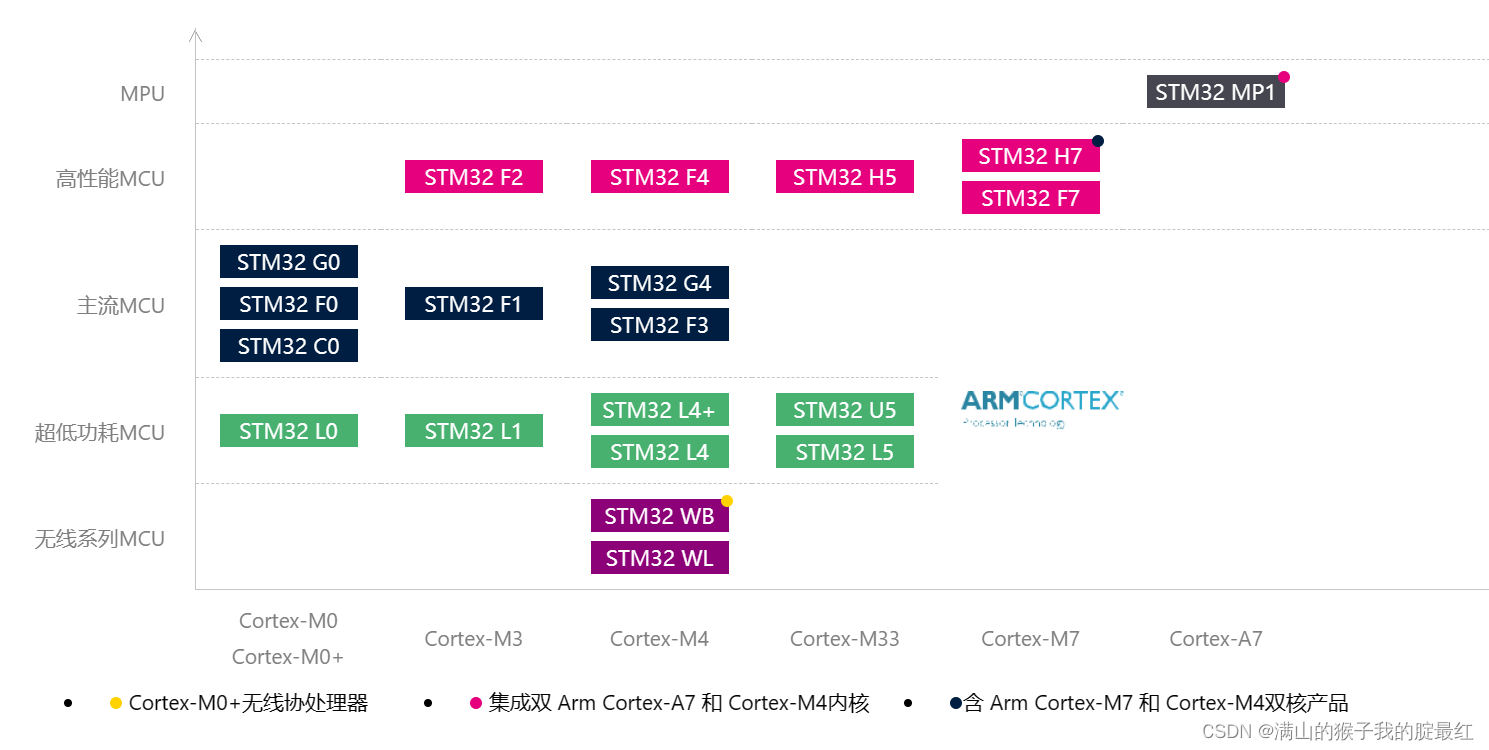

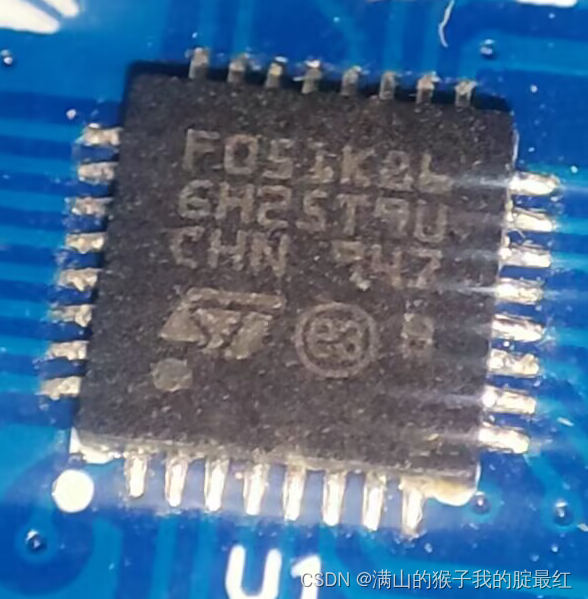

五、STM32介绍

1、 简介

STM32是意法半导体公司生成一款32位的微控制器。

STM32功能强大、性能优异、片上资源丰富、功耗低、是一款经典的嵌入式微控制器。

2、STM32的优势

产品型号丰富,可选择性强;

运算速度快,功耗低;

处理器外设接口丰富;

库函数开发体系学习资料多,应用广泛。

STM32 | 产品 | STM32/STM8 | MCU单片机 | 意法半导体STM | STMCU中文官网

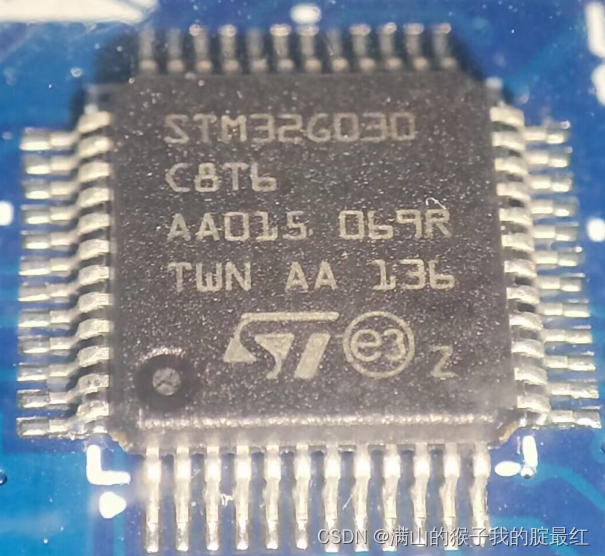

3、 命名规范

STM32F051K8U6

STM32G030C8T6

| ST | 意法半导体 |

| M | 微控制器 |

| 32 | 32位处理器 |

| 类型 | F 通用/基础型 foundation G 多用途型 general-purpose L 低功耗 low power H 高性能 High performance S 简单/标准型 Standard |

| 系列 | 0 精简系列 1/2/3 增强系列 4/7 高性能系列 |

| 子型号 | 00/01/02/03/05/07 |

| 引脚数量 | K/6-32脚 C/8-48脚 R-64脚 V-100脚 Z-144脚 A-168脚 I-176脚 B-208脚 N-216脚 |

| 存储量 | 6 : 32KB 8 : 64KB B :128KB C :256KB D : 384KB E : 512KB G : 1MB I : 2MB |

| 封装 | U - UQFN封装 T - TQFP封装 |

| 工作温度 | 6 - -40 ~ 85度 |

六、ARM体系结构

STM32G030采用ARM Cortex-M0+内核架构

面试题:谈谈你对ARM的认识?

答: 1- ARM是一家公司,ARM公司是一家芯片知识产权(IP)供应商,它与一般的半导体公司最大的不同就是不制造芯片且不向终端用户出售芯片,而是通过转让设计方案,由合作伙伴生产出各具特色的芯片。

2 - ARM处理器,ARM处理器是英国Acorn有限公司设计的低功耗低成本的第一款RISC微处理器。

经典处理器 ARM7\ARM9\ARM11,后续处理器开始以cortex命名

Cortex-A 高性能

Cortex-R 汽车电子

Cortex-M 低成本、低功耗

3 - ARM代表一种技术(精简指令集)。具有性能高、成本低和能耗省的特点。在智能机、平板电脑、嵌入控制、多媒体数字等处理器领域拥有主导地位。

问:目前主流处理器架构?

ARM架构、Intel x86/x64 架构、MIPS架构、RISC-V(开源)

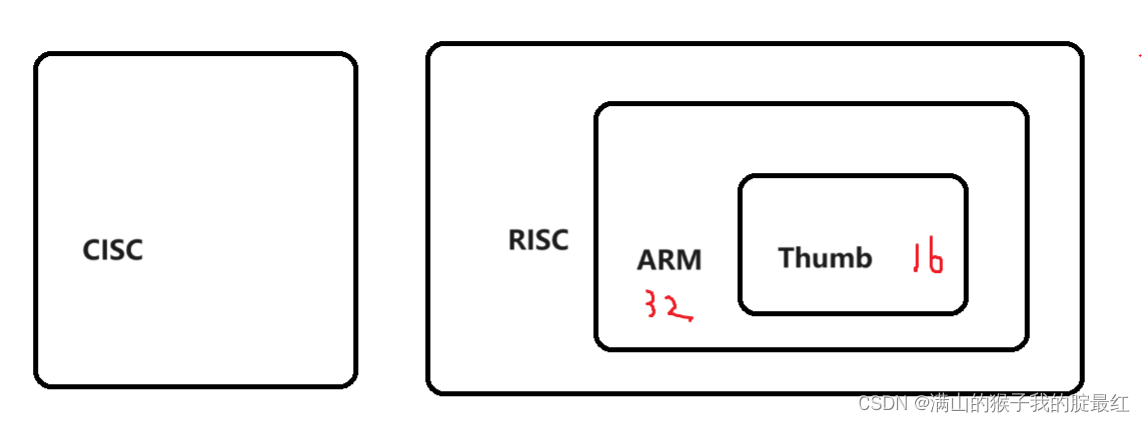

1、 精简指令集(RISC)和复杂指令集(CISC)的区别

早期的CPU全部是CISC架构,它的设计目的是要用最少的机器语言指令来完成所需的计算任务。

比如对于乘法运算,在CISC架构的CPU上,您可能需要这样一条指令:

MUL ADDRA, ADDRB

就可以将ADDRA和ADDRB中的数相乘并将结果储存在ADDRA中。

将ADDRA,ADDRB中的数据读入寄存器,相乘和将结果写回内存的操作全部依赖于CPU中设计的逻辑来实现。

此架构会增加CPU结构的复杂性和对CPU工艺的要求,但对于编译器的开发十分有利

比如上面的例子,C程序中的a*=b就可以直接编译为一条乘法指令。

今天只有Intel及其兼容CPU还在使用CISC架构。

RISC架构要求软件来指定各个操作步骤。上面的例子如果要在RISC架构上实现,将ADDRA, ADDRB中的数据读入寄存器,相乘和将结果写回内存的操作都必须由软件来实现

比如:

MOV A, ADDRA;

MOV B, ADDRB;

MUL A, B;

STR ADDRA,A

此架构可以降低CPU的复杂性以及允许在同样的工艺水平下生产出功能更强大的CPU,但对于编译器的设计有更高的要求。

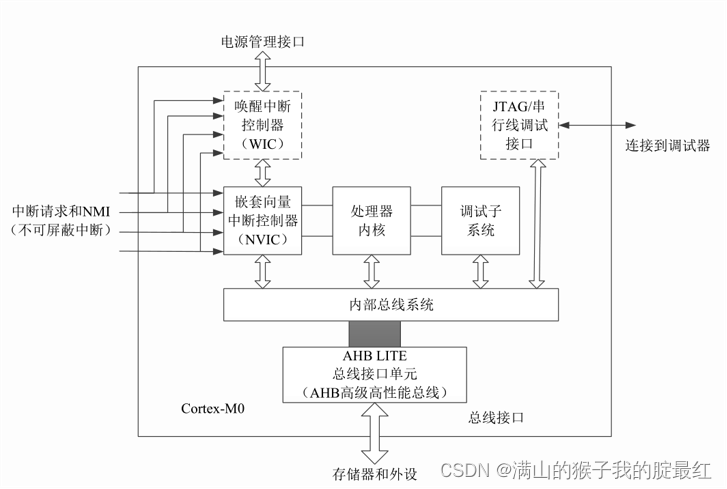

2、Cortex-M0架构框图

Cortex-M0 微处理器主要包括处理器内核、嵌套向量中断控制器(NVIC)、调试子系统、内部总线系统构成。Cortex-M0 微处理器通过精简的高性能总线(AHB-LITE)与外部进行通信。

扩展:架构

冯诺依曼架构

冯·诺依曼体系结构,冯·诺依曼理论的要点是:计算机的数制采用二进制;计算机应该按照程序顺序执行。冯·诺依曼结构的处理器使用同一个存储器,经由同一个总线传输。

哈佛架构

哈佛结构的计算机由CPU、程序存储器和数据存储器组成,哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,程序存储器和数据存储器采用不同的总线,从而提供了较大的存储器带宽,使数据的移动和交换更加方便,尤其提供了较高的数字信号处理性能。

二者的区别就是程序空间和数据空间是否是一体的。

冯·诺依曼结构数据空间和地址空间不分开,哈佛结构数据空间和地址空间是分开的。

主要区别就是命令/数据总线

3、Cortex-M0的指令集

ARM处理器支持两种指令集:ARM 和 Thumb。

EPSR寄存器的T标志位负责指令集的切换,Cortex-M0只支持Thumb指令。

ARM指令集 32位精简指令集; 指令长度固定;

降低编码数量产生的耗费,减轻解码和流水线的负担;

Thumb指令集指令宽度16位;

Thumb指令集是ARM指令集的一个子集;

与32位指令集相比,大大节省了系统的存储空间;(密度高)

Thumb指令集不完整,所以必须配合ARM指令集一同使用

问:Thumb指令集和ARM指令集的区别?

关系、区别、优缺点

4、Cortext-M0特性

- 采用Thumb指令集 (ARM指令是32位的,而Thumb指令时16位的,如果存储空间中可以放32条ARM指令,就可以放64条Thumb指令,因此在存放Thunb指令时,代码密度高)

- 高性能,使用ARMv6-M的体系架构;

- 中断数量可配置1-32个,4级中断优先级

- 门电路少,低功耗 中断唤醒控制器(WIC),支持极低功耗休眠模式

- 兼容性好 与Cortex-M1 处理器兼容,向上兼容 Cortex-M3 和 Cortex-M4 处理器 ,可以很容易地升级、移植。

- 支持多种嵌入式操作系统(RTOS),也被多种开发组件支持

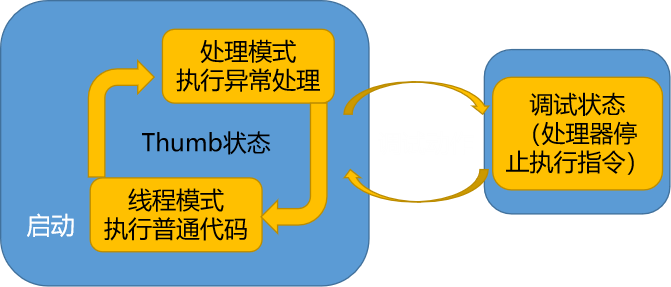

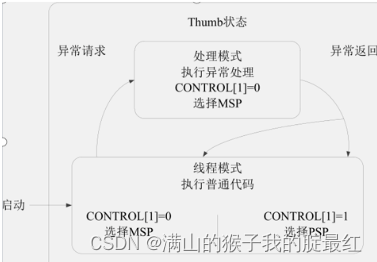

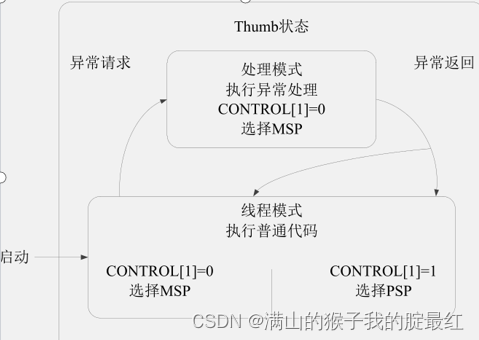

5、Cortex-M0工作模式

线程模式(Thread Mode)- 芯片复位后,执行用户程序

处理模式(Handler Mode)- 当处理器发生了异常或者中断,处理完成后返回线程模式。

6、Cortex-M0工作状态

Thumb状态:正常运行时处理器的状态

调试状态:调试程序时处理器的状态

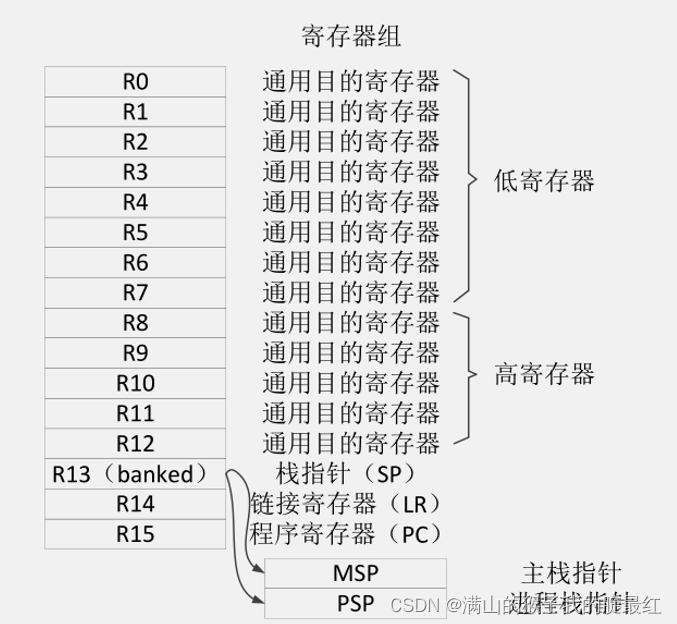

7、Cortex-M0的寄存器

(1)通用寄存器

- ARM内部还有这些东西

- 通用寄存器R0-R12

13个通用寄存器。其中 R0-R7为低端寄存器,可作为16位或32 位指令操作数,R8-R12为高端寄存器,只能用作32位操作数

- SP堆栈指针 R13

栈指针寄存器 SP(the stark pointer),Cortex-M0 在不同物理位置上存在两个栈指针,主栈指针 MSP,进程栈指针 PSP(CONTROL寄存器 控制两个进程栈切换)

在处理模式下,只能使用主堆栈,在线程模式下,可以使用主堆栈也可以使用进程堆栈。 系统上电的默认栈指针是MSP。这样设计的目的是为了在进行模式转换的时候,减少堆栈的保存工作。同时也可以为不同权限的工作模式设置不同的堆栈。

- LR链接寄存器 R14

用于存储子程序或者函数调用的返回地址

- PC程序计数器 R15

存储下一条将要执行的指令的地址。

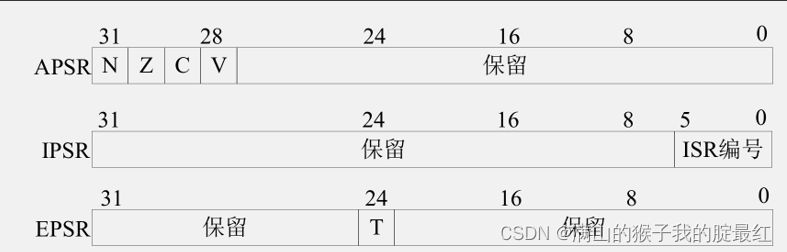

- xpsr组合程序状态寄存器

-

- APSR包含前一条指令执行后的条件标志 N Z C V

保存程序计算结果的状态标志 N负数标志 Z零标志 C进位借位标志 V溢出标志

-

- IPSR包含ISR的异常编号

包含当前ISR的异常编号

-

- EPSR包含Thumb状态位

-

- PRIMSK中断屏蔽特殊寄存器

- CONTROL

MSP 0 PSP 1

- 异常和中断 简单说一嘴->后面中断再详细说

【STM32教程】一文搞懂ARM内核是如何控制外设寄存器的_stm32 系统控制寄存器_小超电子笔记的博客-CSDN博客

(2)特殊寄存器

xPSR:组合程序状态寄存器,该寄存器由三个程序状态寄存器组成

应用PSR(APSR):保存程序计算结果的状态标志 N负数标志 Z零标志 C进位借位标志 V溢出标志

中断PSR(IPSR):包含当前ISR(中断状态寄存器)(中断服务程序)的异常编号

执行PSR(EPSR):包含Thumb状态位

CONTROL:控制寄存器

控制处理器处于线程模式时,使用哪个堆栈

=0,使用MSP 处理器模式时,固定使用MSP

=1,使用PSP

8、 Cortex-M0的中断和异常

Cortex-M0 处理器最多支持32个外部中断(通常称为 IRQ)和一个不可屏蔽中断(NMI),另外Cortex-M0还支持许多系统异常(Reset、HardFault、SVCall、PendSV、SysTick),它们主要用于操作系统和错误处理

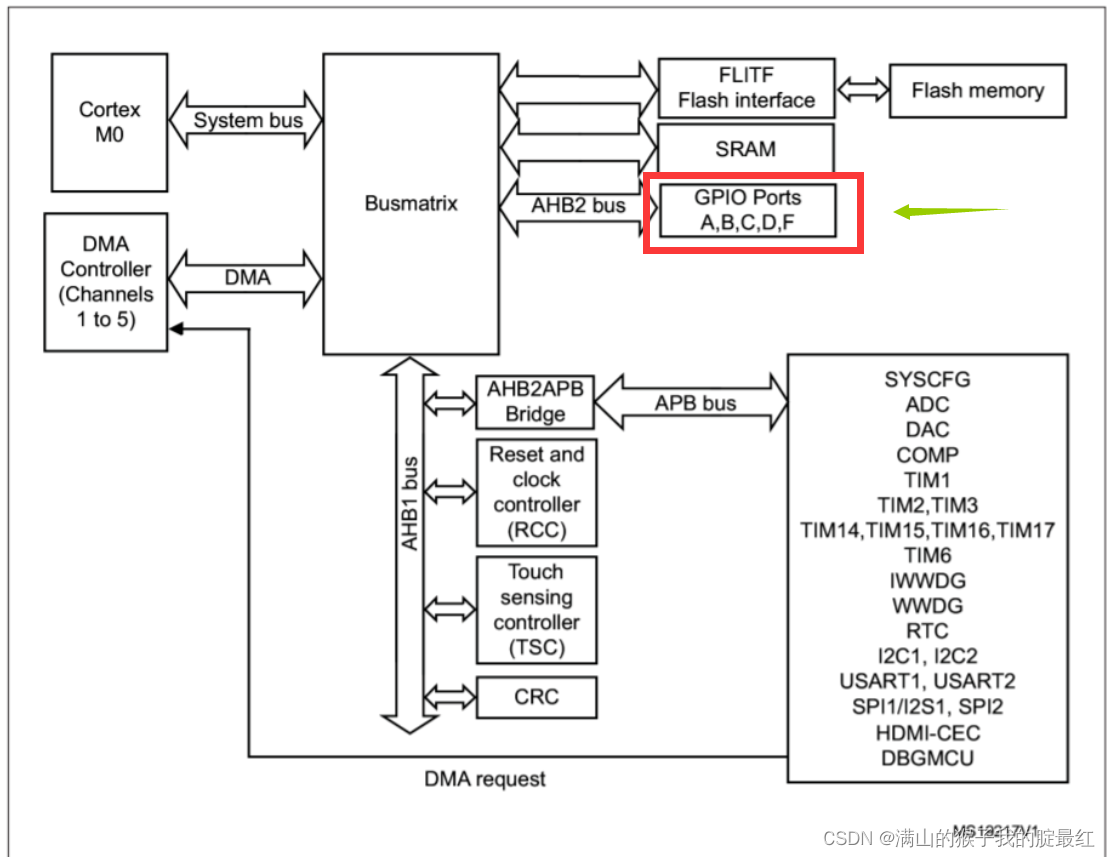

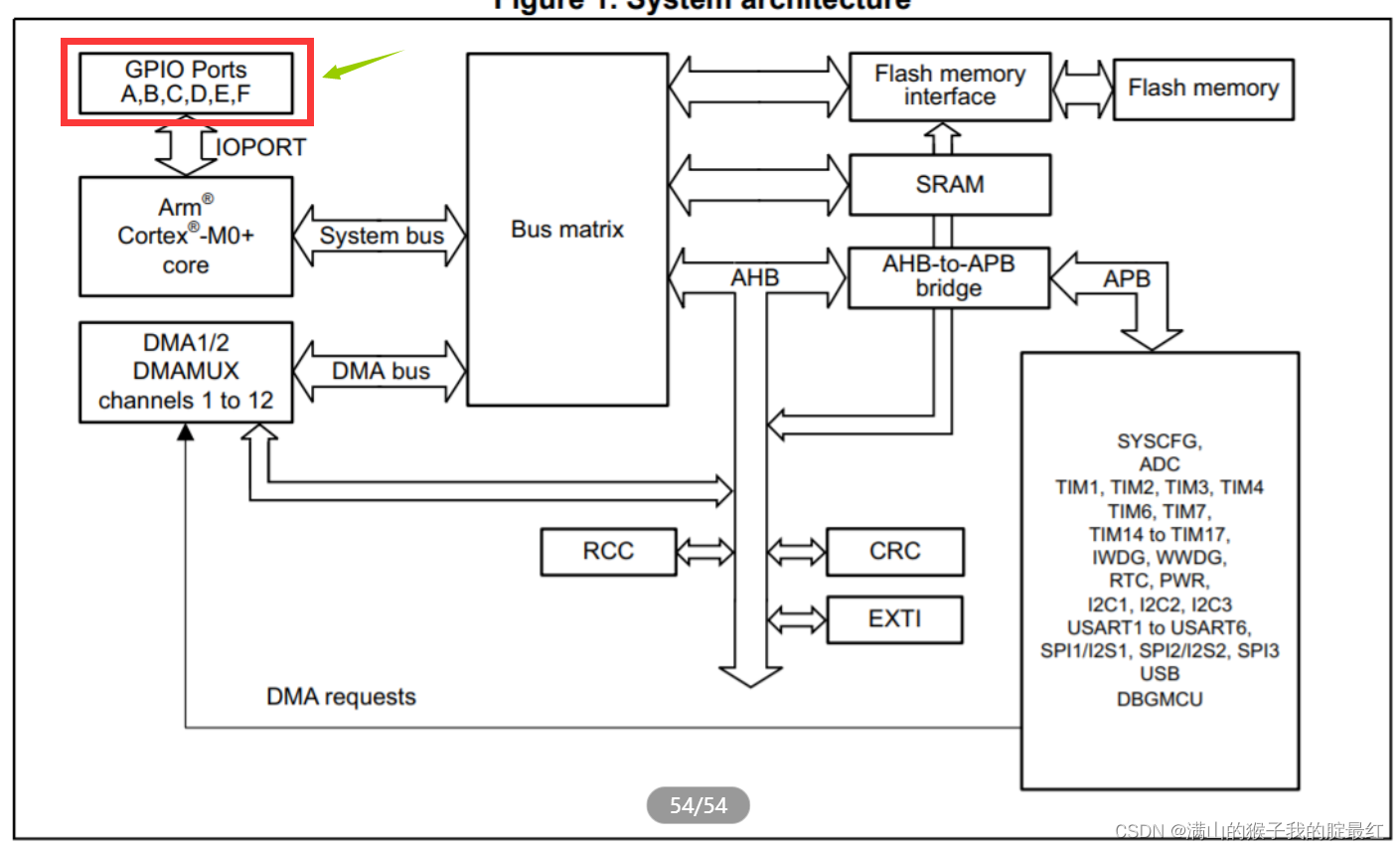

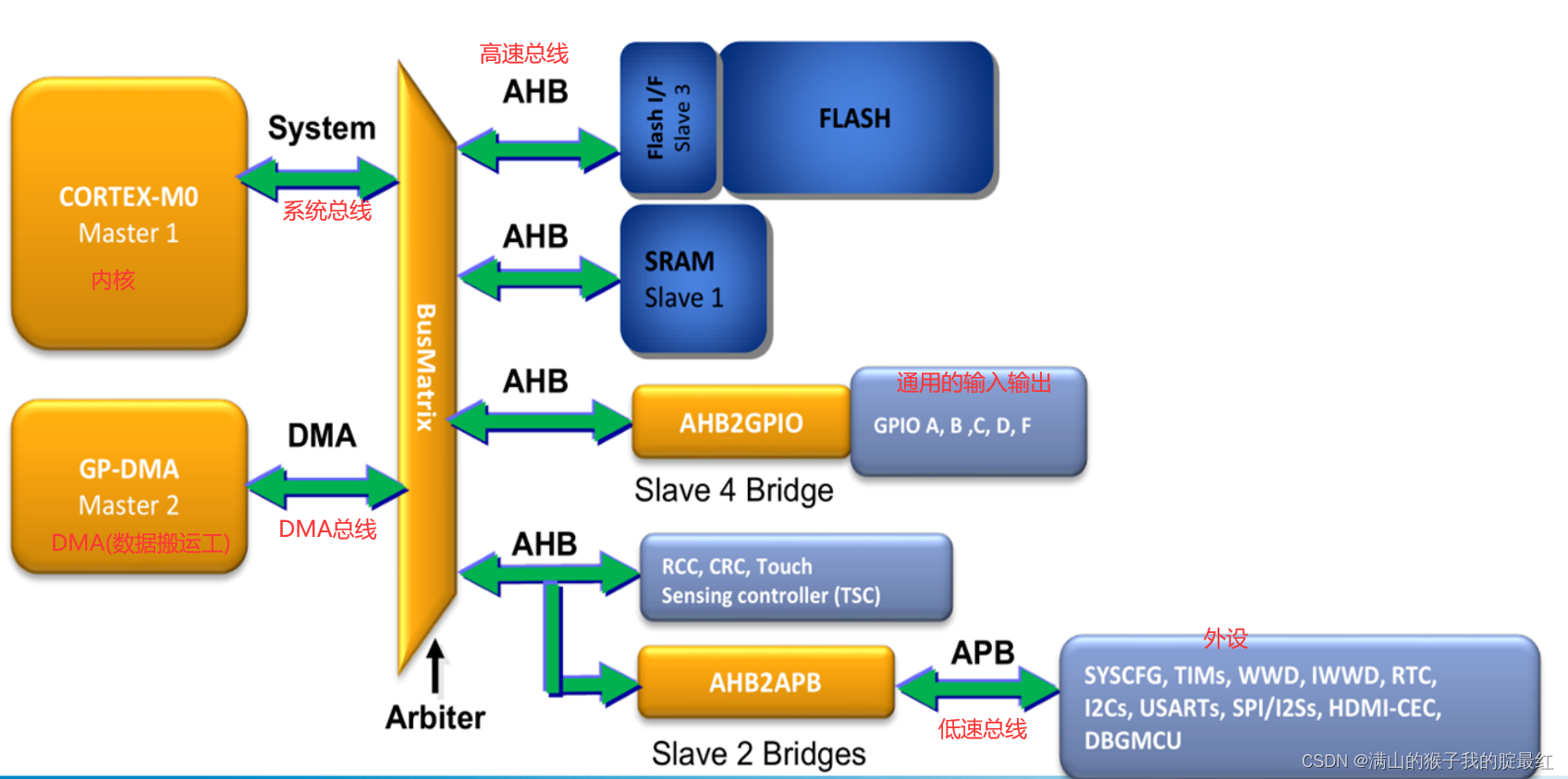

9、 STM32G030系统架构

处理器架构

STM32F0

STM32G0

系统主要由以下几个模块组成 :

● 二个主模块 :

– Cortex-M0 内核及先进高性能总线 (AHB bus)

– 通用 DMA ( GP-DMA -- general-purpose DMA)

● 四个从模块 :

– 内部 FLASH

– 内部SRAM

– APB桥,连接AHB和APB,所有的外设都挂在APB总线上

G0: GPIOx直接挂在IOPORT总线上。

F0 : 专门用于连接GPIO口的AHB2总线

问:flash和SRAM的区别?

Flash存储器是一种非易失性存储器,可以在掉电之后保存数据,通常用于存储程序代码。Flash存储器的可写入次数有限,且需要执行擦除操作才能写入新的数据,因此,在使用过程中需要注意擦写周期和数据备份问题。

SRAM存储器则是一种易失性存储器,具有相对较快的读写速度和无限的读写次数,但掉电时将会丢失所有内容。SRAM存储器主要用于暂存数据和临时变量,读写操作由CPU直接完成,访问速度较快。

单片机的Flash存储器和SRAM存储器通常都嵌入在单片机芯片内部,能够方便地实现对程序和数据的读写操作。通常,编译器会将程序代码烧录到Flash存储器中,并使用SRAM存储器来存储变量、函数堆栈和其他临时数据。

问:什么是外设?如何理解片上外设?

与传统的外设不同,片上外设通常具有以下优点:

高效性:片上外设能够与主处理器实现高速的数据传输,响应时间短,执行效率高。

集成度高:片上外设多个模块都嵌入到处理器芯片内部,极大地降低了PCB面积和电路复杂度。

低功耗:处理器和片上外设采用相同的工艺,能够满足高密度和低功耗的需求。

可靠性高:提高了整体系统的可靠性和稳定性,也降低了电磁干扰的可能。

问:AHB和APB的区别?

AHB是高速总线,是一种系统总线,它主要负责连接处理器、DMA等一些内部接口。AHB系统由主模块、从模块和基础结构3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

APB是低速总线,它主要负责连接外围设备,它又分为APB1和APB2,它的总线架构不像 AHB支持多个主模块,在APB里面唯一的主模块就是APB桥。

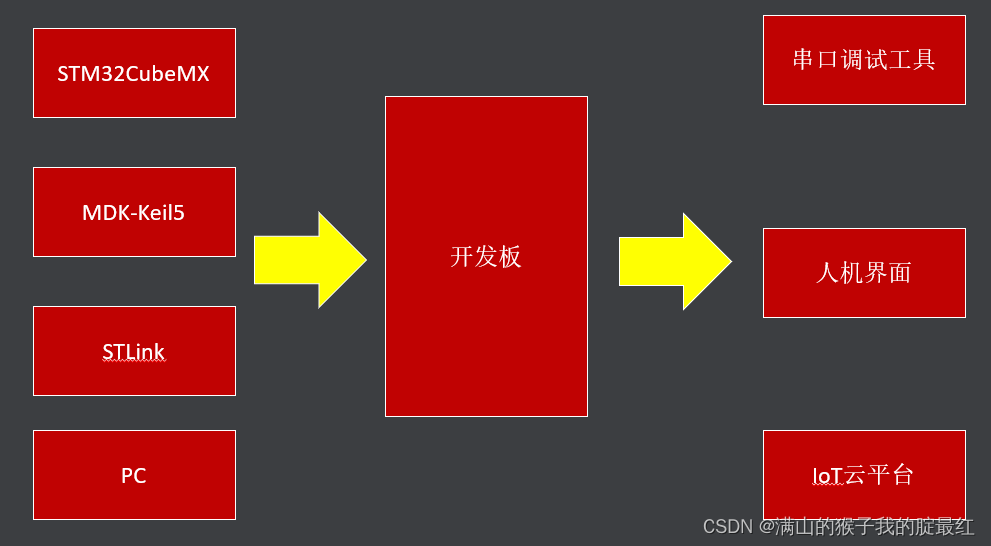

七、如何开发

八、开发环境搭建

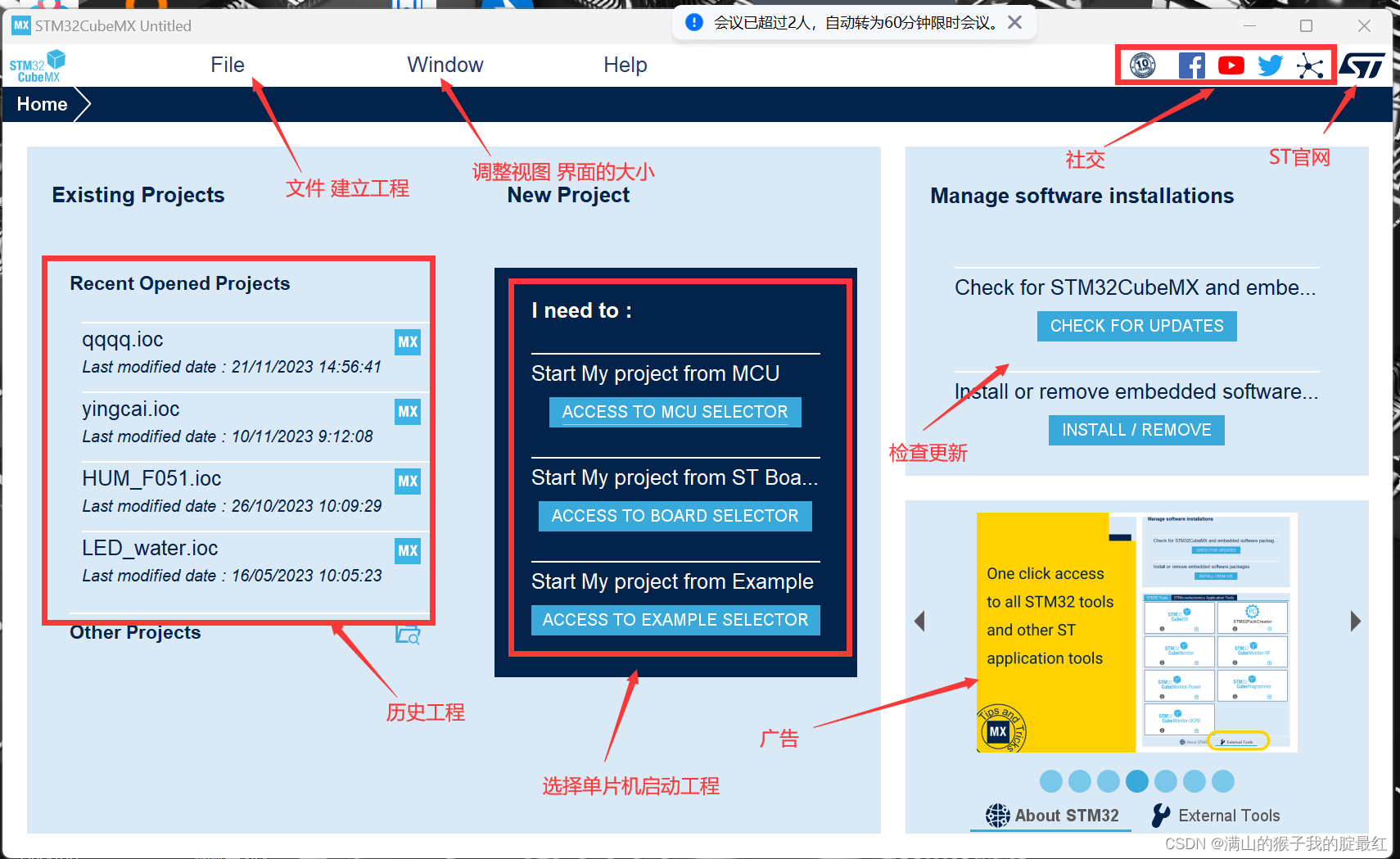

1 STM32CubeMX

ST公司出品 工具链接

工具链接 https://www.st.com/zh/development-tools/stm32cubemx.html

STM32CubeMX是一种图形工具,通过分步过程可以非常轻松地配置STM32微控制器和微处理器,以及为Arm® Cortex®-M内核或面向Arm® Cortex®-A内核的特定Linux®设备树生成相应的初始化C代码。

作用及功能:

(1)工程项目搭建和配置

(2)直观选择微控制器

(3)图形化引脚功能配置、引脚冲突提示

(4)动态配置时钟树

(5)动态设置参数和初始化

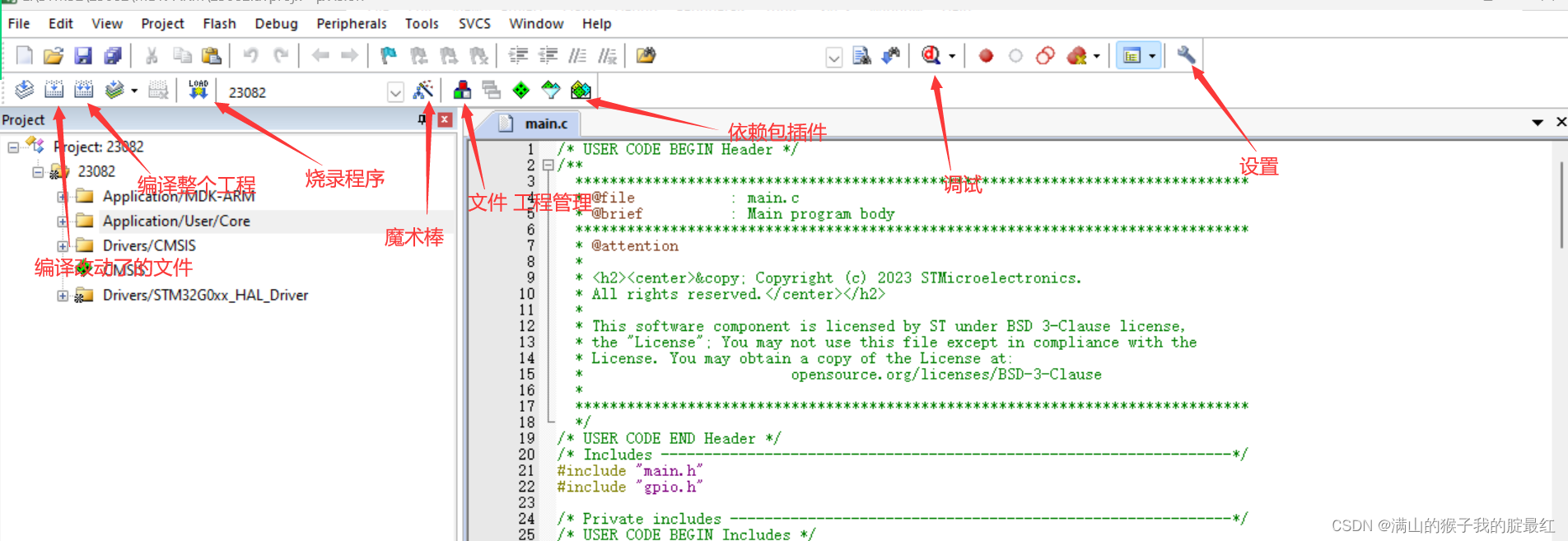

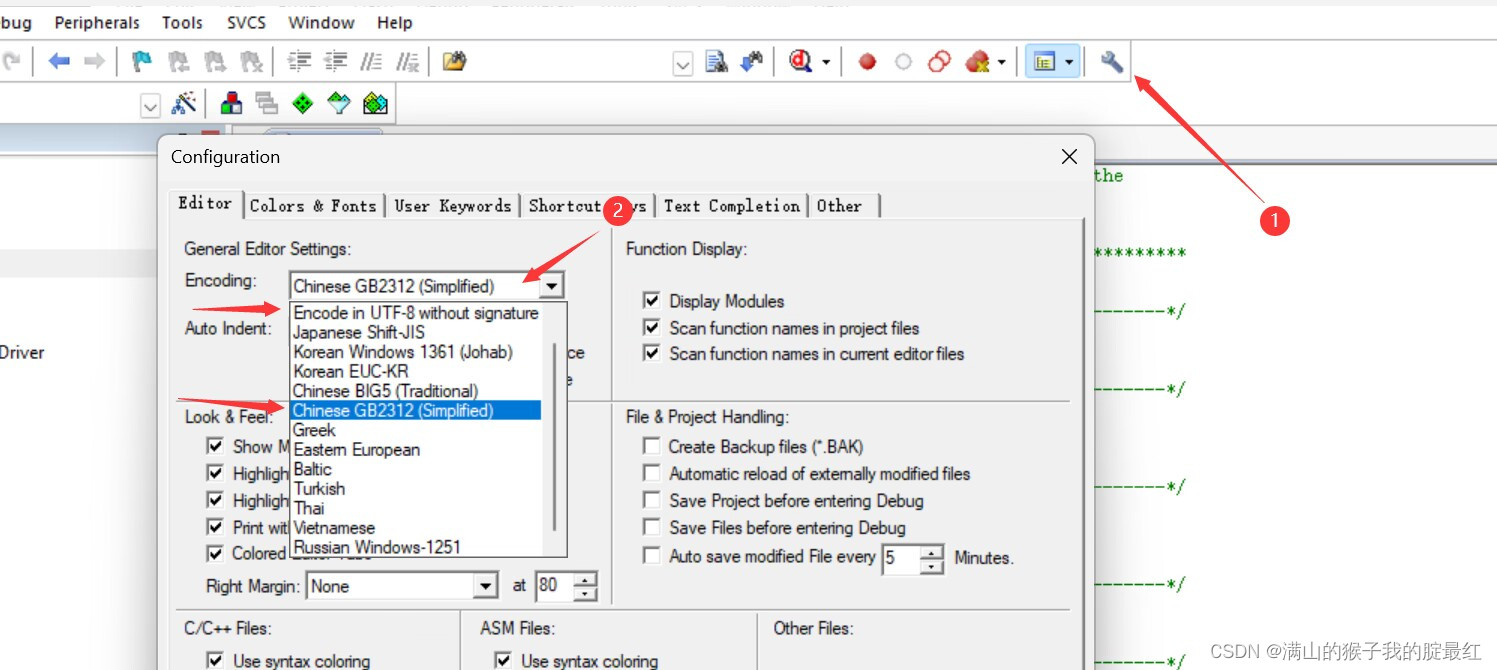

2 Keil安装

Keil μVision 5 也称MDK-ARM、Realview MDK

MDK ——》Microcontroller Development Kit

MDK包含以下几个部分:

μVision5:一种集成开发环境,提供了多种不同的功能,如编辑器、编译器、调试器等。

ARM编译器:一种嵌入式ARM C / C++编译器,可在多种不同的微控制器平台上运行。

Device Family Pack:一种特定于属于不同微控制器平台/系列/型号的软件包,包括库文件、设备描述文件等。

Debugger:一款高级调试器,支持多种不同的调试功能,如单步调试、断点调试、内存映射等。

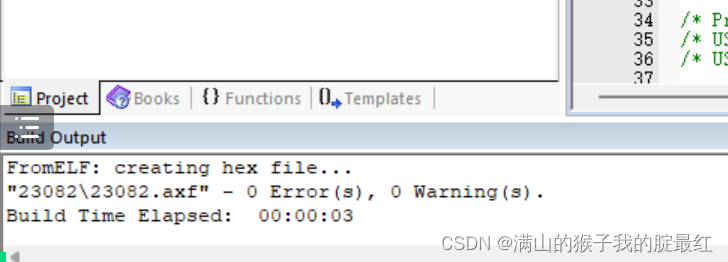

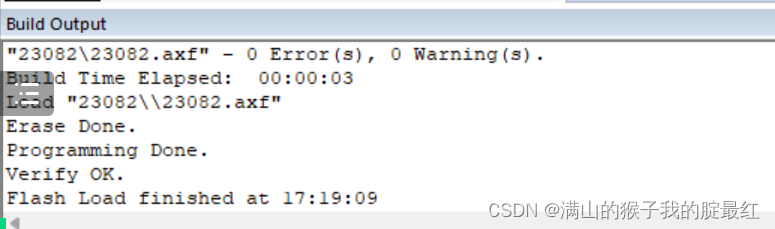

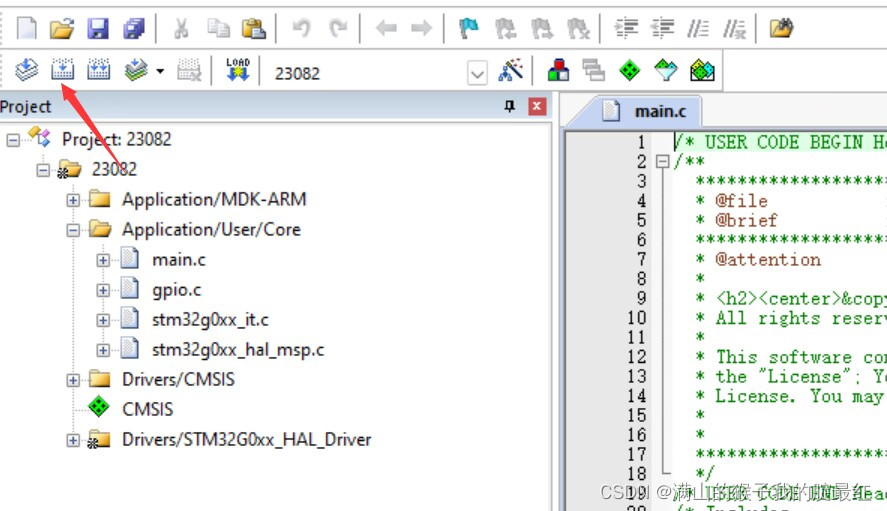

九、创建STM32工程

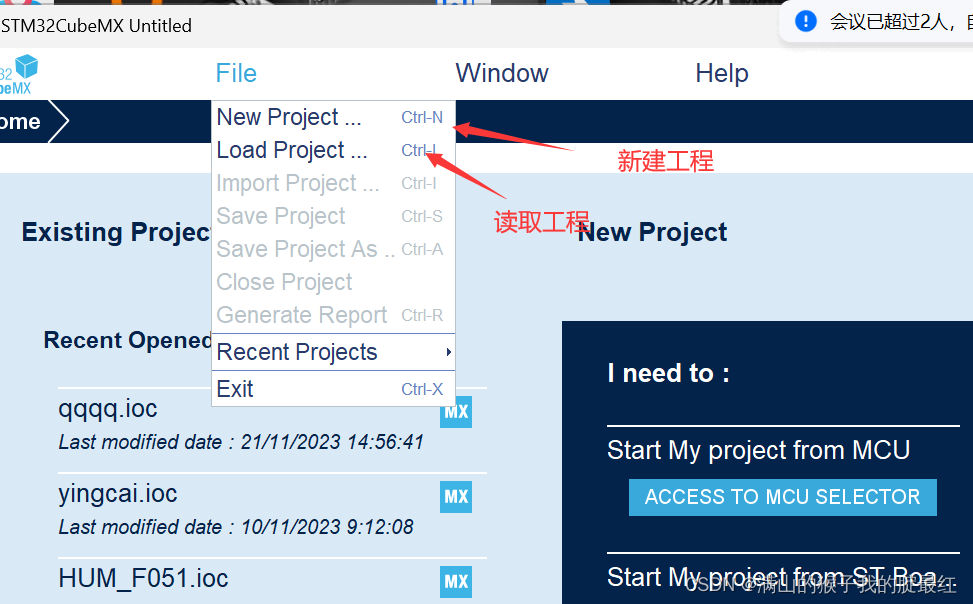

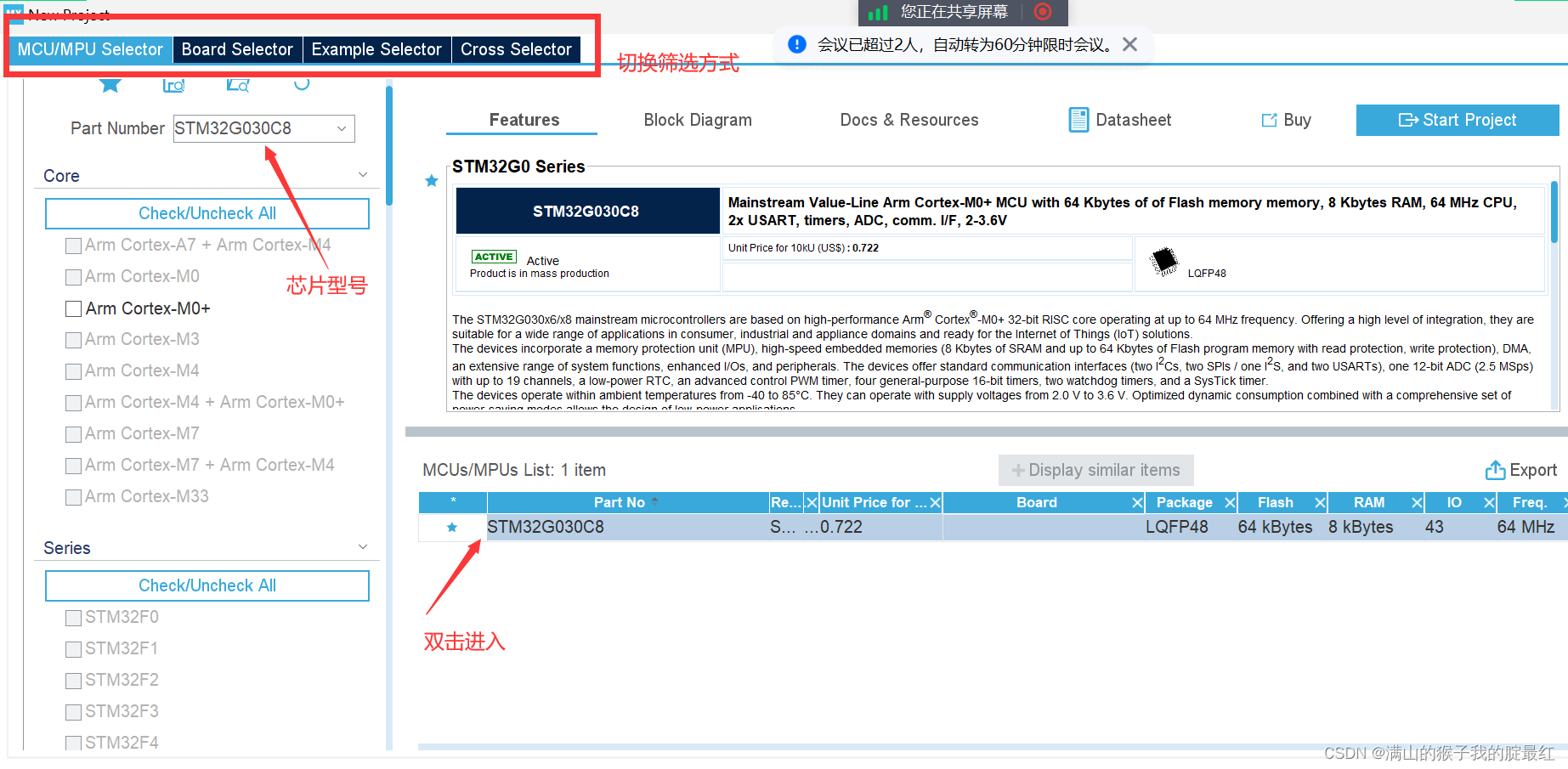

STM32CubeMX介绍

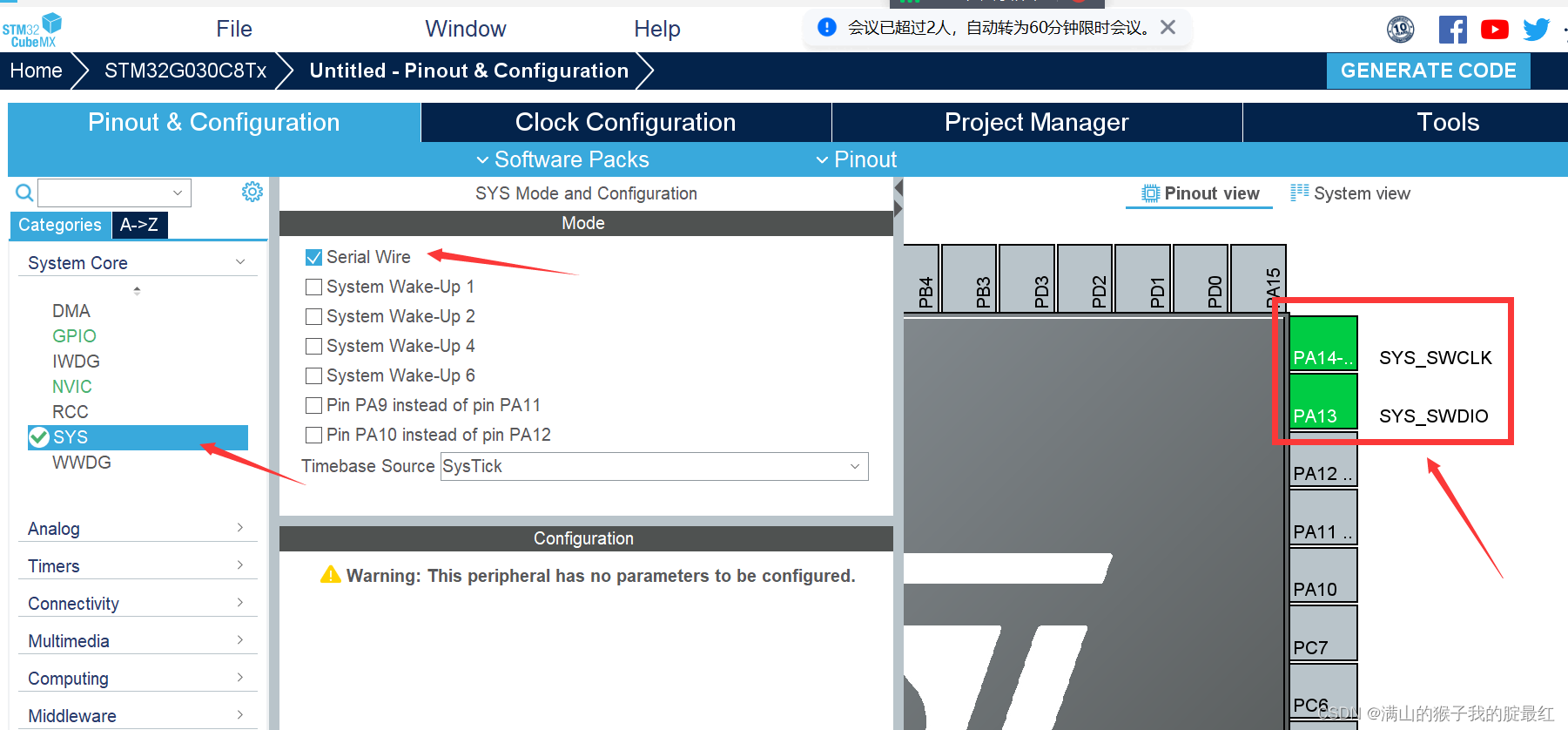

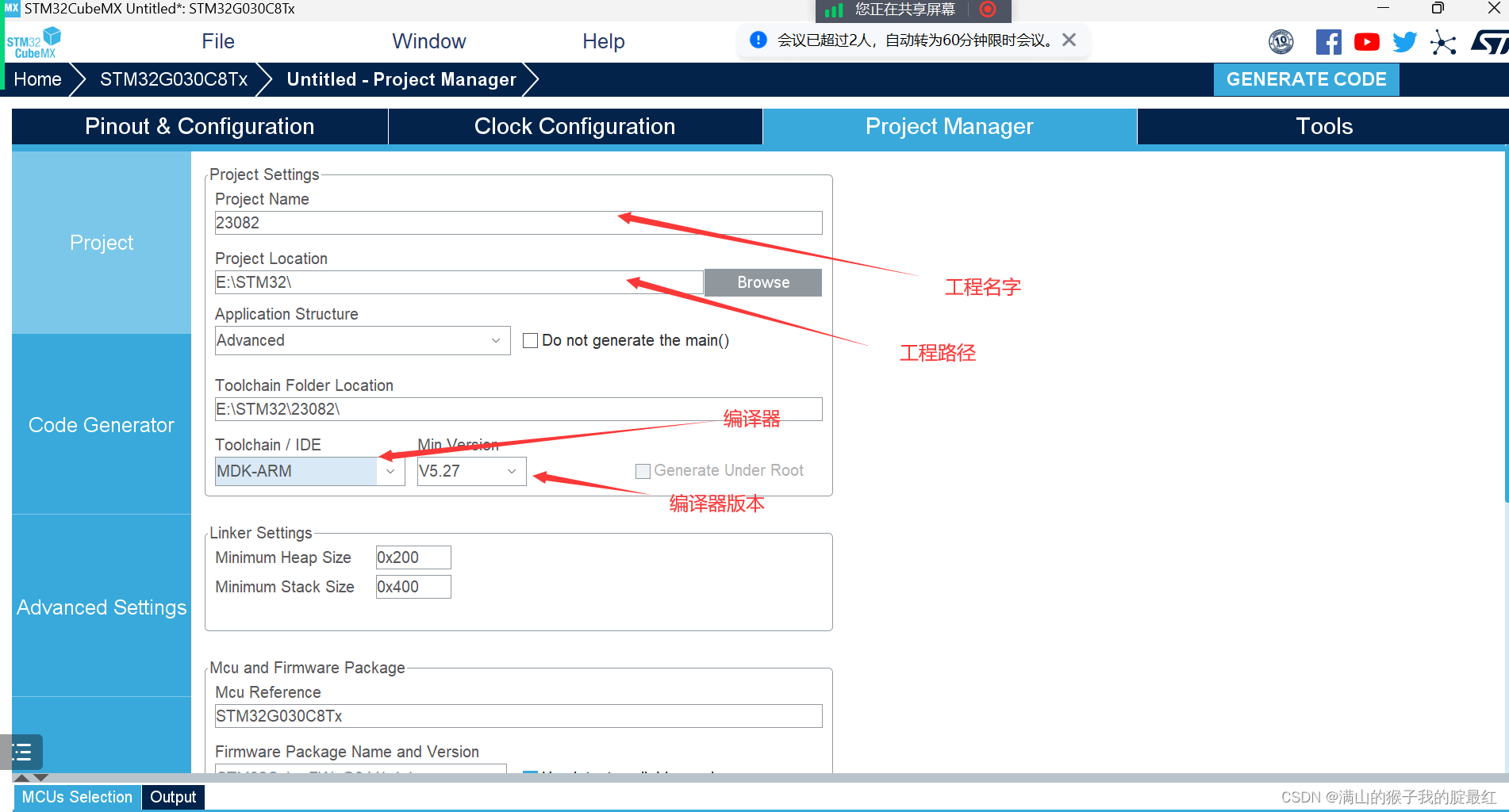

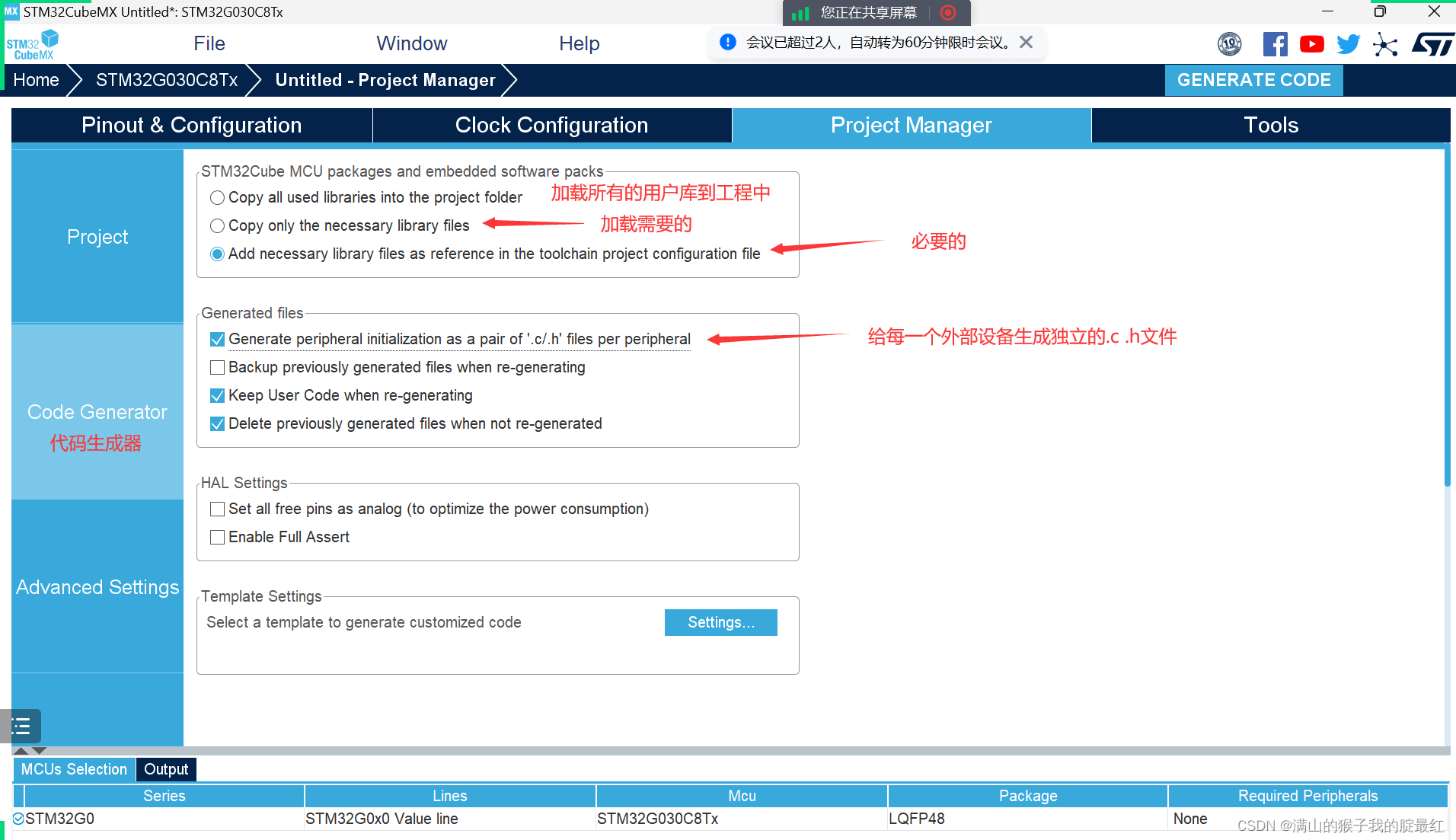

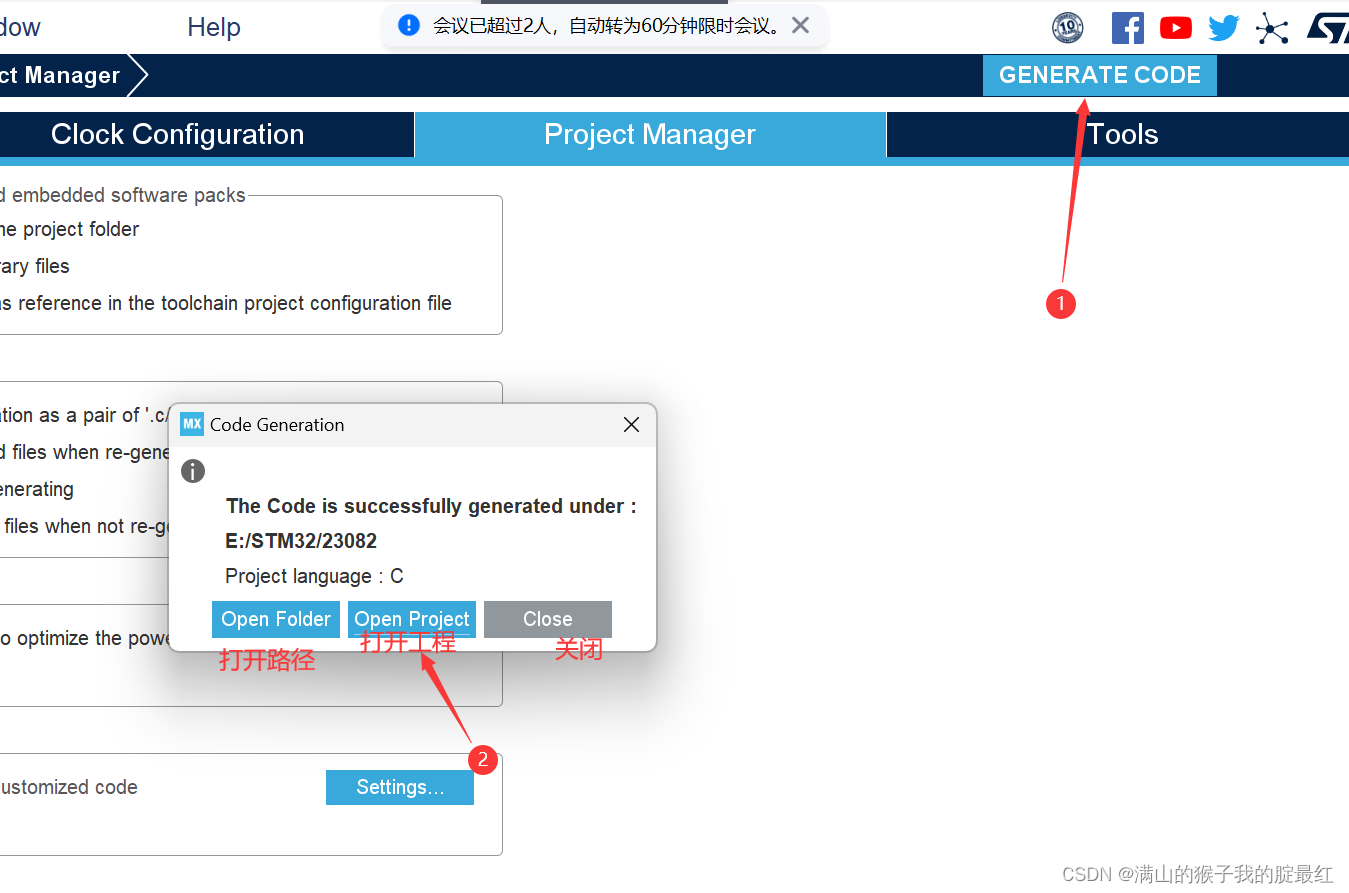

注意:选好自己的芯片之后,这里记得勾选上。防止第二次烧录程序,烧录失败。课程上使用的芯片不勾选也没关系。

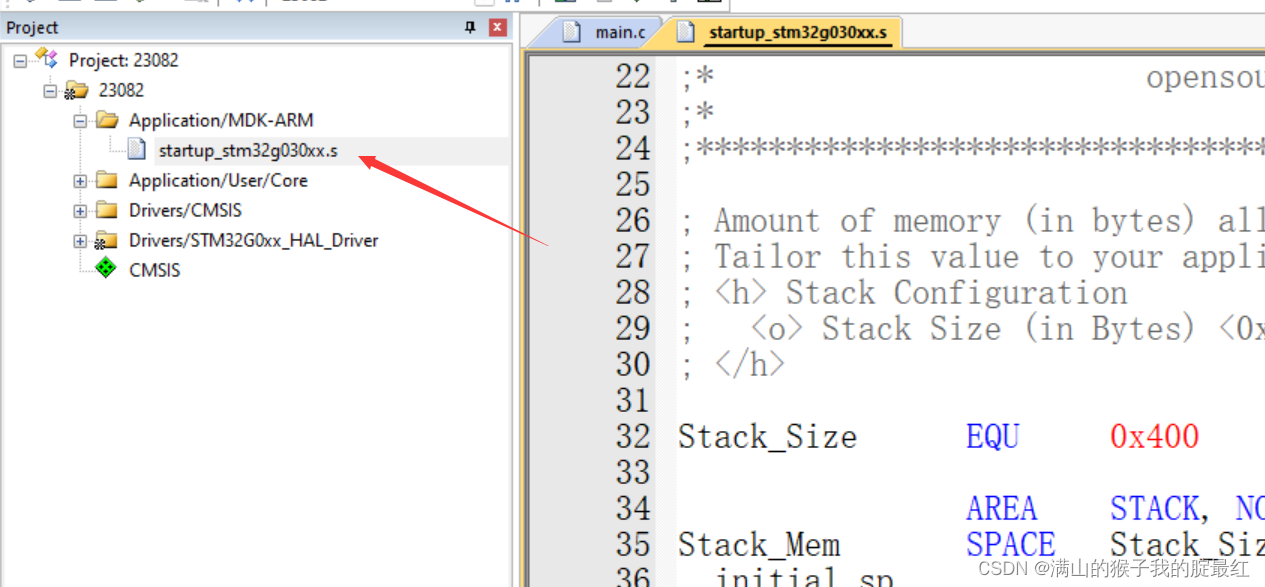

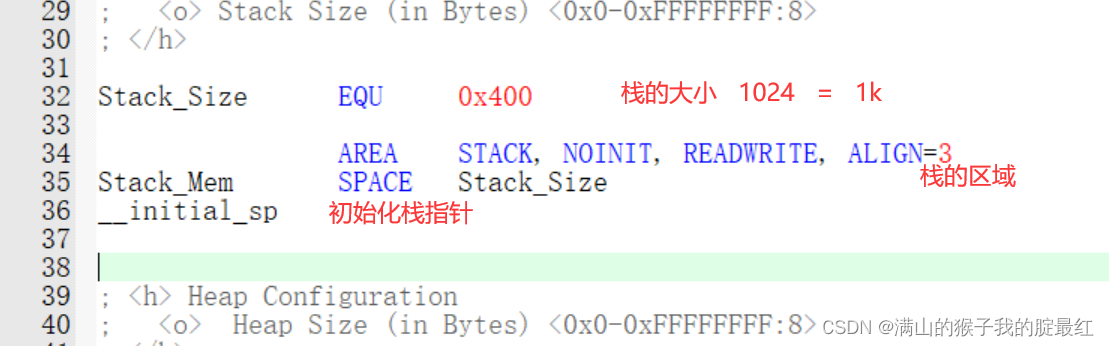

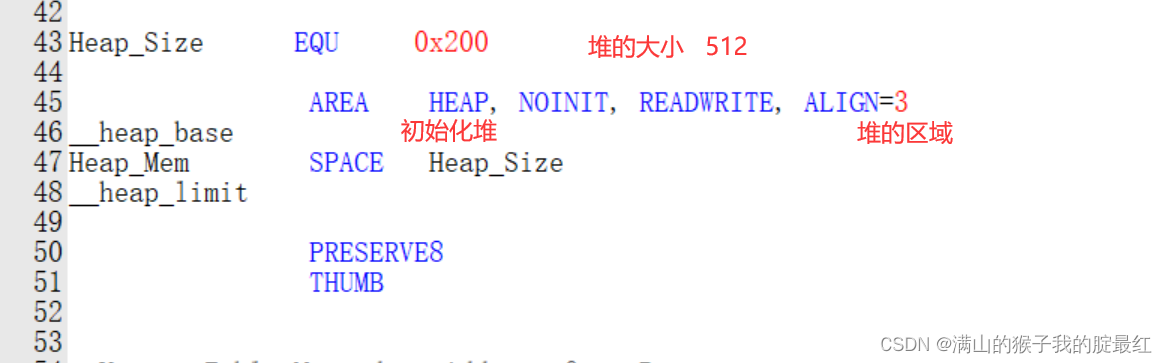

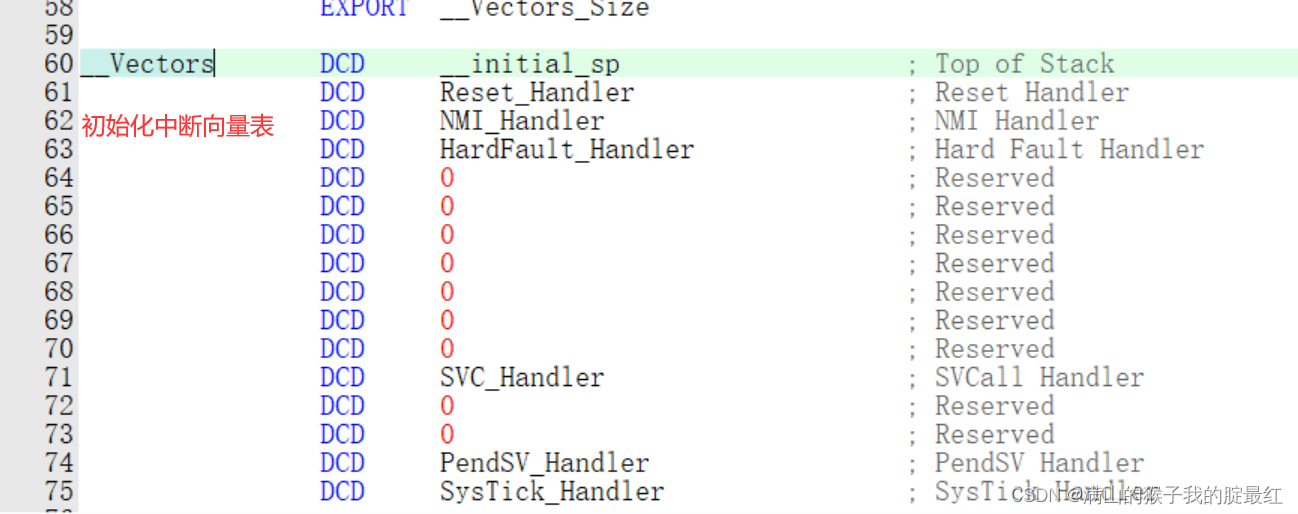

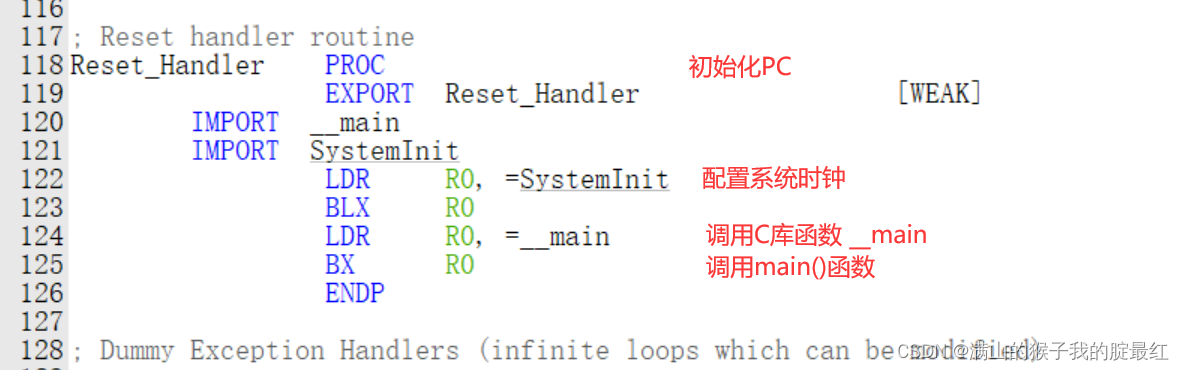

- 单片机上电后第一个执行的程序

1、初始化堆栈指针SP=_initial_sp

2、初始化PC 指针=Reset_Handler

3、初始化中断向量表

4、配置系统时钟SystemInit

5、调用C 库函数__main 初始化用户堆栈,从而最终调用main 函数去到C 的世界