在现代计算机系统中,缓存(Cache)的性能对于整个系统的性能至关重要。工程师们在设计和优化缓存系统时,经常面临一系列挑战和问题,这些问题直接影响到处理器的效率、系统的响应速度以及能源的消耗。

以下是一些工程师们在缓存设计中经常遇到的问题:

缓存缺失(Cache Miss):当处理器需要的数据不在缓存中时,会导致缓存缺失,这会显著降低性能,因为必须从较慢的主存中获取数据。

缓存一致性(Cache Coherence):在多核处理器系统中,保持缓存之间的数据一致性是一个复杂的问题,需要高效的一致性协议来解决。

缓存污染(Cache Pollution):某些数据模式可能导致缓存中存储大量不必要的数据,从而降低了缓存的有效性。

缓存大小限制:缓存的大小受限于成本和物理空间,但更大的缓存通常能提供更高的命中率。

写策略选择:写回(Write-back)和写直通(Write-through)策略各有优缺点,选择合适的写策略对性能有重要影响。

预取算法效率:有效的预取算法可以减少缓存缺失,但设计高效的预取算法是一个挑战。

多端口缓存设计:在需要同时处理多个数据流的系统中,如何设计多端口缓存以提高带宽和降低延迟。

面对这些挑战,我们如何提高缓存的性能呢?

提高缓存(Cache)性能是计算机体系结构设计中的一个核心目标。3C定理(也称为Cache容量、Cache一致性、Cache并行性定理)是关于计算机系统缓存性能的一个重要理论,它指出了影响缓存性能的三个主要因素:容量(Capacity)、一致性(Consistency)和并行性(Concurrency)。

No.1 容量(Capacity)

增大缓存大小:增加缓存的容量可以减少对主存储的访问次数,从而提高性能。

合理的缓存行大小:选择合适的缓存行大小可以提高缓存的命中率。

多层缓存:使用多级缓存结构(如L1、L2和L3缓存)可以进一步提高性能。

No.2 一致性(Consistency)

缓存一致性协议:在多处理器系统中,采用有效的缓存一致性协议(如MESI协议)可以确保数据的一致性,避免数据不一致导致的性能下降。

写策略:选择合适的写策略(如写回或写直通)可以影响缓存的一致性和性能。

No.3 并行性(Concurrency)

多端口缓存:支持多端口访问的缓存可以同时处理多个请求,提高并行性。

预取技术:使用预取技术可以提前加载数据,减少CPU等待时间。

锁定策略:合理的锁定策略可以减少在高并发访问时的争用。

而在现代计算机体系结构中,多端口设计、多发射指令和异常处理是提高处理器性能和稳定性的关键技术。

多端口CacheMultiple-port Cache

一种允许多个硬件模块或处理器核心同时访问同一Cache存储的体系结构。这种设计在需要高带宽和低延迟数据访问的系统中尤为重要。

以下是一些多端口Cache的应用场景:

多处理器系统:允许多个CPU核心同时访问共享缓存。

图形处理:GPU需要同时处理多个纹理和顶点数据。

网络设备:路由器和交换机需要同时处理多个数据包。

优势:提高了数据带宽和处理能力。减少了因资源争用导致的延迟。

在设计使用多端口Cache的系统时,需要考虑Cache的一致性、替换策略、带宽分配以及硬件的复杂性等问题。尽管多端口Cache的设计和实现可能更加复杂,但它为需要高并发数据访问的系统提供了显著的性能优势。

多发射指令Multiple Instruction Issue

多发射技术允许CPU在每个时钟周期内发射(即执行)多条指令,这是超标量架构的一个特征,旨在提高指令执行的并行度。

实现方式:

硬件资源重复:CPU中有多套执行单元,可以同时处理不同类型的指令。

指令调度:通过复杂的调度算法,CPU可以在每个周期选择多条独立(无数据或控制依赖)的指令进行发射。

优势:提高了指令执行的吞吐量。更好地利用了CPU内部的硬件资源。

异常处理Exception Handling

异常处理是计算机系统中对异常情况(如违反访问权限、算术溢出、页面错误等)的响应机制。

处理流程:

异常检测:当异常情况发生时,硬件或操作系统需要能够检测到它。

上下文保存:保存当前的执行状态,如寄存器内容和程序计数器。服务例程调用:跳转到异常或中断服务例程,处理异常情况。

上下文恢复:处理完毕后,恢复保存的上下文,继续执行或退出异常。

优势:保证了系统的稳定性和数据的一致性。允许系统从错误中恢复,而不是直接崩溃。

工程师在掌握了如何优化和提高缓存性能后,是否还面临以下问题:

01、初学Cache设计很难理解多个层面的硬件架构和工作原理?

02、学习了相关理论课程,但在实际项目中应用时面临很多问题,如性能瓶颈、资源限制等

03、理论经验丰富,但缺乏工程实践和项目经验,难以获得面试机会!

以上问题都在阐述着实战项目的缺乏针对问题所在,在此推荐芯片前端技术专题《Cache设计》

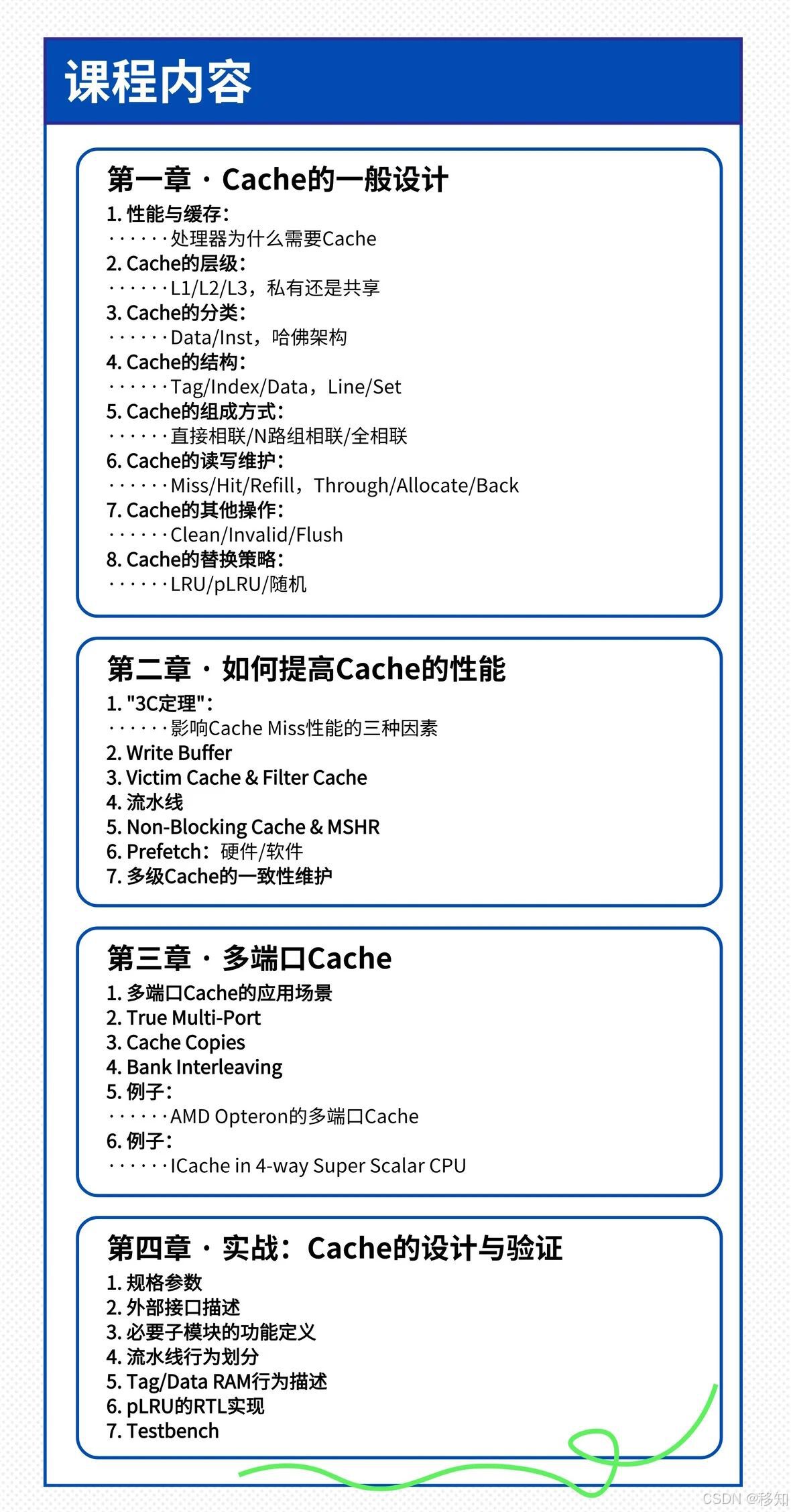

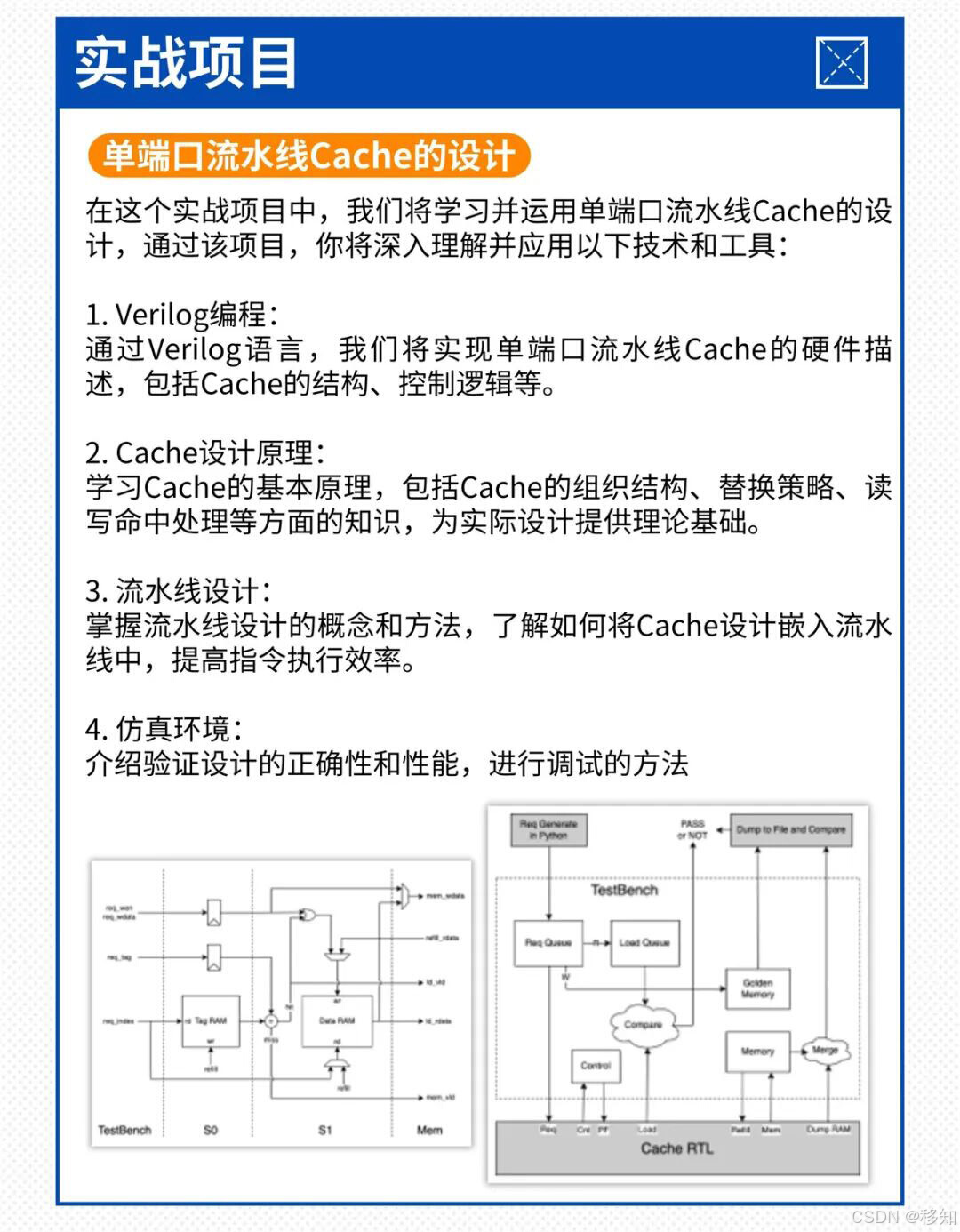

学员通过专题课程,学习掌握不同类型的Cache结构和实现,含多端口Cache、多发射等,理解Cache的基本原理和各个组成部分的功能。掌握状态机设计和流水线优化的理论基础,设计更高效的硬件状态机和流水线结构,掌握异常处理和缺失处理的策略。

培养专业能力,全面掌握验证与测试策略,保证硬件设计的质量。掌握优化方法,进行性能和时序面积优化。

随着Cache的深入探讨,我们希望大家都能够对Cache技术有一个全面而深刻的理解。通过结合理论知识与实际应用案例,帮助大家不仅掌握Cache的基本概念,而能够灵活地将其应用于解决实际问题中。