一、说明

I2C(Inter-Integrated Circuit)其实是IICBus简称,所以中文应该叫集成电路总线,它是一种串行通信总线,使用多主从架构,由飞利浦公司在1980年代为了让主板、嵌入式系统或手机用以连接低速周边设备而发展。

I2C是一种同步串行总线,总共有两根线:SDA和SCL,其中数据SDA可以双向传输,时钟SCL只能从主到从(外带控制器的不算,这种架构不太常用,正文也不考虑)。常用的I2C总线都是OD开漏输出,因此需要电路上增加上拉电阻。

I2C支持两种寻址方式,分别是7bit地址和10bit的地址,其中7bit地址是常用且必须支持的,10bit地址一般不用,是一个可选的功能,具体看芯片规格书。

二、协议介绍

协议要求,数据传输时,数据SDA在时钟SCL高电平时务必保持电平稳定,不能有高低电平切换,切换只能发生在时钟SCL处于低电平非采样时进行。

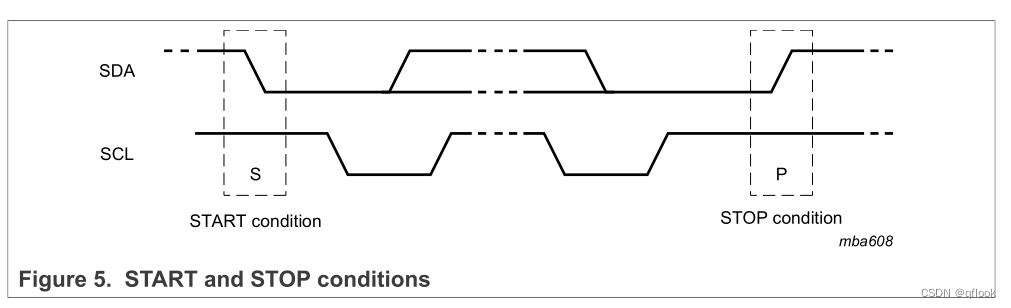

1.START和STOP

所有事件必须以START(S)开始,以STOP(P)结束。其中START是在时钟SCL处于高电平状态时,数据SDA从高电平变成低电平;STOP是时钟SCL处于高电平状态时,数据SDA从低电平变成高电平。具体如下图:

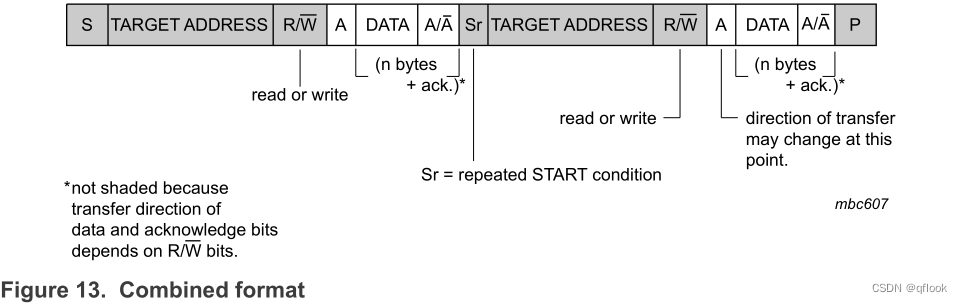

START和STOP只能是Master产生,另外在STOP之前可以有多个START,除了第一个START外的开始均成 repeated START (Sr)。

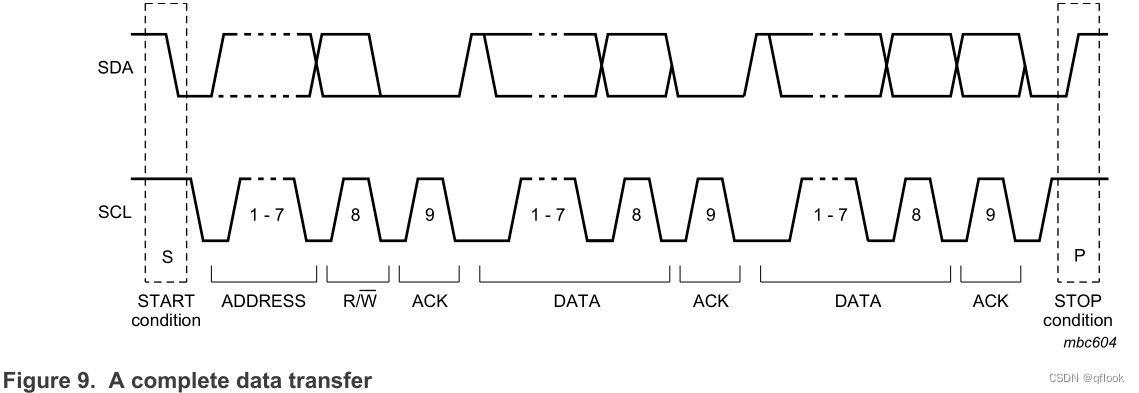

2.数据帧

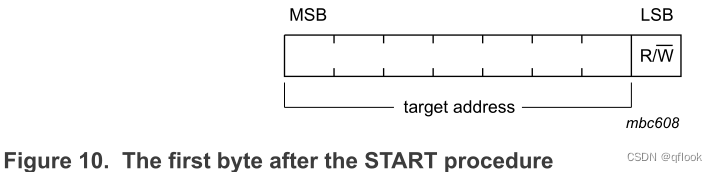

I2C的帧必须8bit长度,但每次传输的帧数量没有限制,每8bit数据后必须有一个Acknowledge bit(简称ACK)。数据传输时,高位先发,也就是第一位是最高位MSB,第8位是最低位LSB。

3.ACK和NACK

3.ACK和NACK

数据传输时,第9位是0就代表是ACK,本数据是接收数据的设备(可能是Master也可能是Slave)产生,含义是接收成功;如第9位是1就代表是NACK,含义是接收异常(接收器处于忙状态无法处理或者地址错误没有响应等),这时Master可以产生STOP结束通讯,也可以发送repeated START (Sr)以重新发送。

接收异常主要包括:

-

接收器正在处理无法处理数据;

-

地址错误导致无设备响应(没有从设备拉低SDA信号线);

-

接收到的数据或命令不能被理解;

-

接收器无法接收更多的数据等。

4.仲裁Arbitration

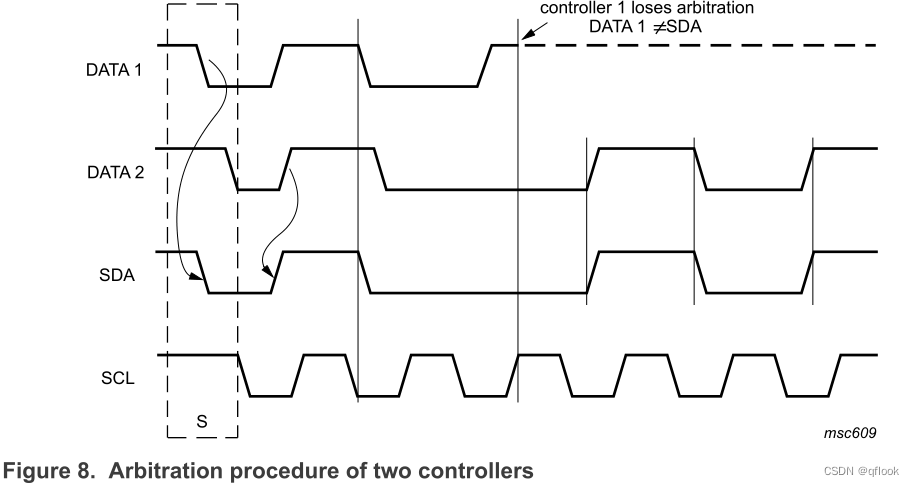

仲裁只有在多个Master的情况下才会遇到,即两个或多个Master在START的最小保持时间 (tHD;STA )内都控制SDA从高电平变成低电平。仲裁只支持标准模式、快速模式和快速plus模式,不支持高速和超快速模式。

仲裁是通过处理每个bit的方式进行,直到有Master控制SDA先变成高电平,则判另一个Master抢占总线成功,如下图,Master2最后仲裁成功:

5.设备地址和R/W位

5.设备地址和R/W位

7bit的设备地址是在START信号后发送,第8位就是读写位,其中1是读指令,0是写指令:

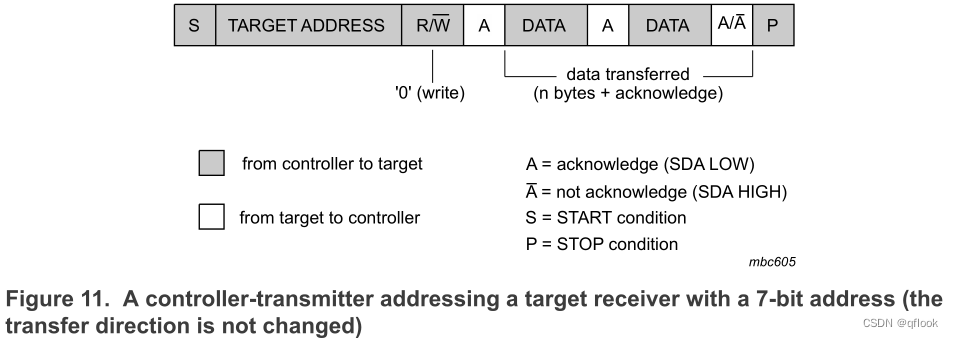

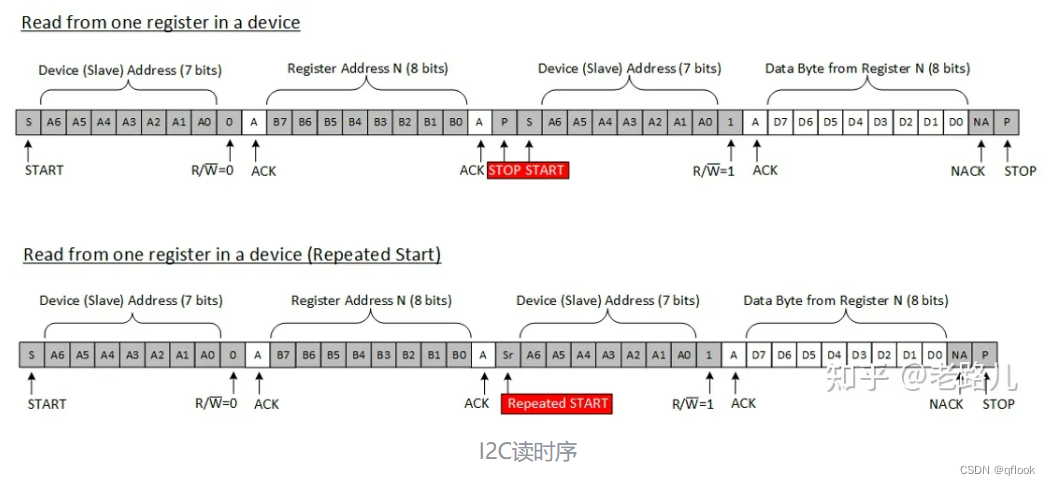

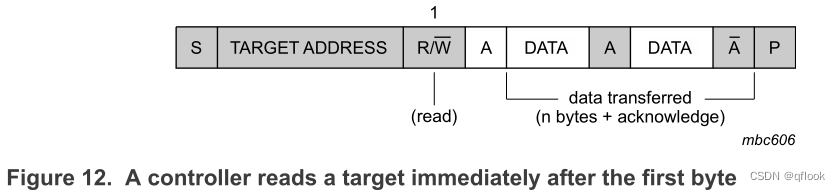

需注意,当是读指令时,后边的DATA就是Slave产生,如是写指令,则继续是Master产生DATA。如下:

协议上对这部分写的不是很详细,大家对比看下其他人写的资料,注意两点,其一是读写切换可以中间用STOP也可以用RE-START信号,其二是读操作时,在STOP信号前Master发送的应答是NACK:

设备地址除了常用的7bit格式外,还有不常用的10bit格式,这里就简单介绍下,由于10bit地址用1个字节(8bit)传输不够,用2个字节就少了5bit(R/W占了1bit),协议规定发送10bit地址时前面补充11110,如下:

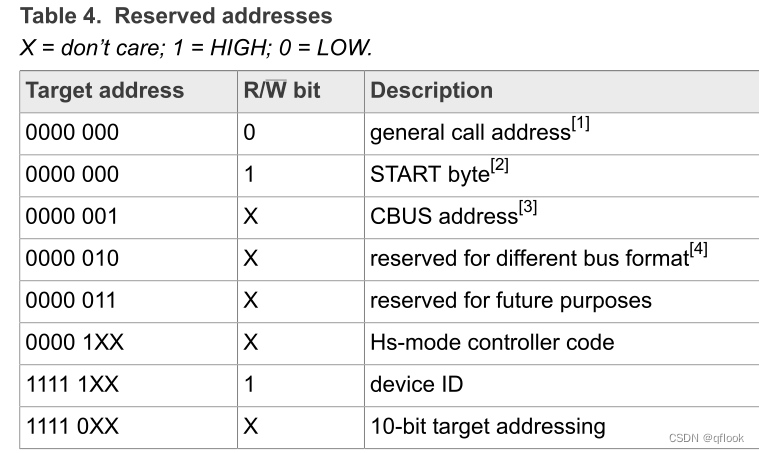

6.保留地址

0000 XXX and 1111 XXX的地址是特别预留的,有特定含义,具体如下,本文不再展开讲了:

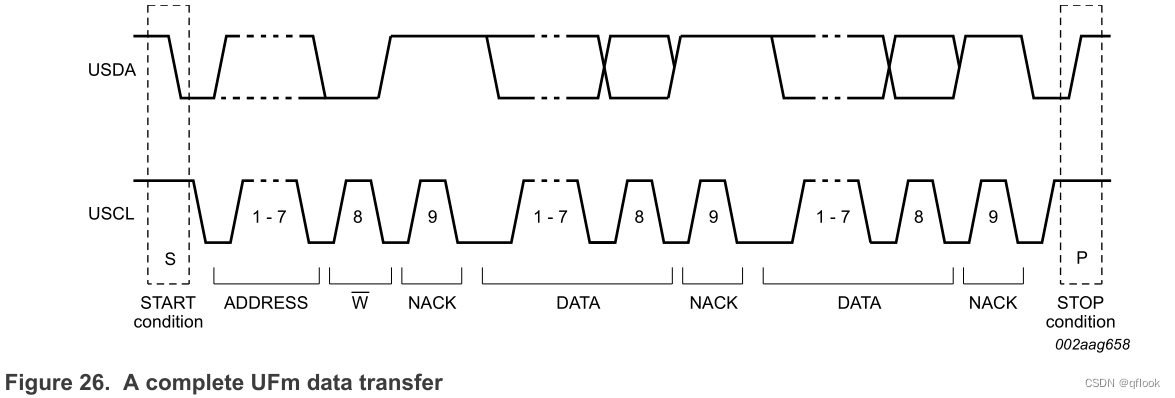

7.超快Ultra Fast-mode I2C

支持更高速率的Ultra Fast-mode和普通I2C有一定区别:

-

SDA是单向传输,因此R/W信号只支持0(写),不支持1(读);

-

SDA和SCL是推挽输出,不再是开漏OD输出,因此不需要上拉电阻;

-

没有ACK,只有NACK,也就是第9位SDA只能是高电平1;

8.高速模式Hs-mode

高速模式除了提供比较快的数据通讯速率外,还可以向下兼容。但是本模式不支持仲裁和时钟同步功能。

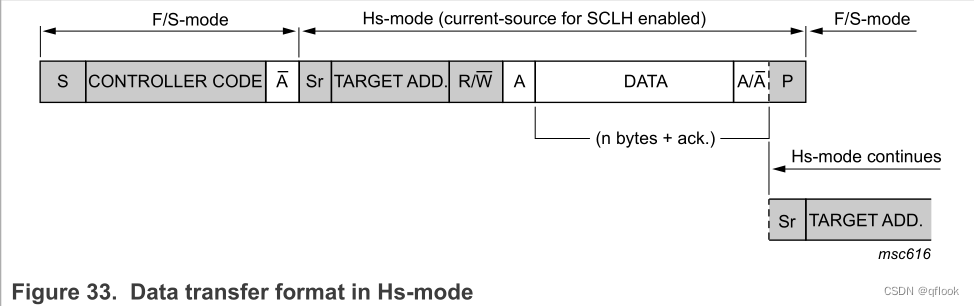

本模式传输时,必须首先发送高速模式控制码00001XXX,具体帧格式:START信号+高速模式控制码+NACK,如下图:

三、时序及信号电平要求

1.信号电平

无论何种模式,信号电平的VIL的范围是【-0.5V,0.3VDD】,VIH的范围是【0.7VDD,min(VDD+0.5V,5.5V)】。

2.普通模式时序要求

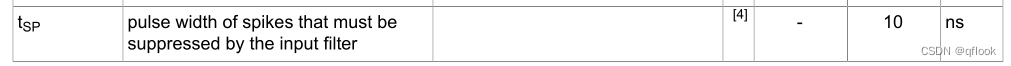

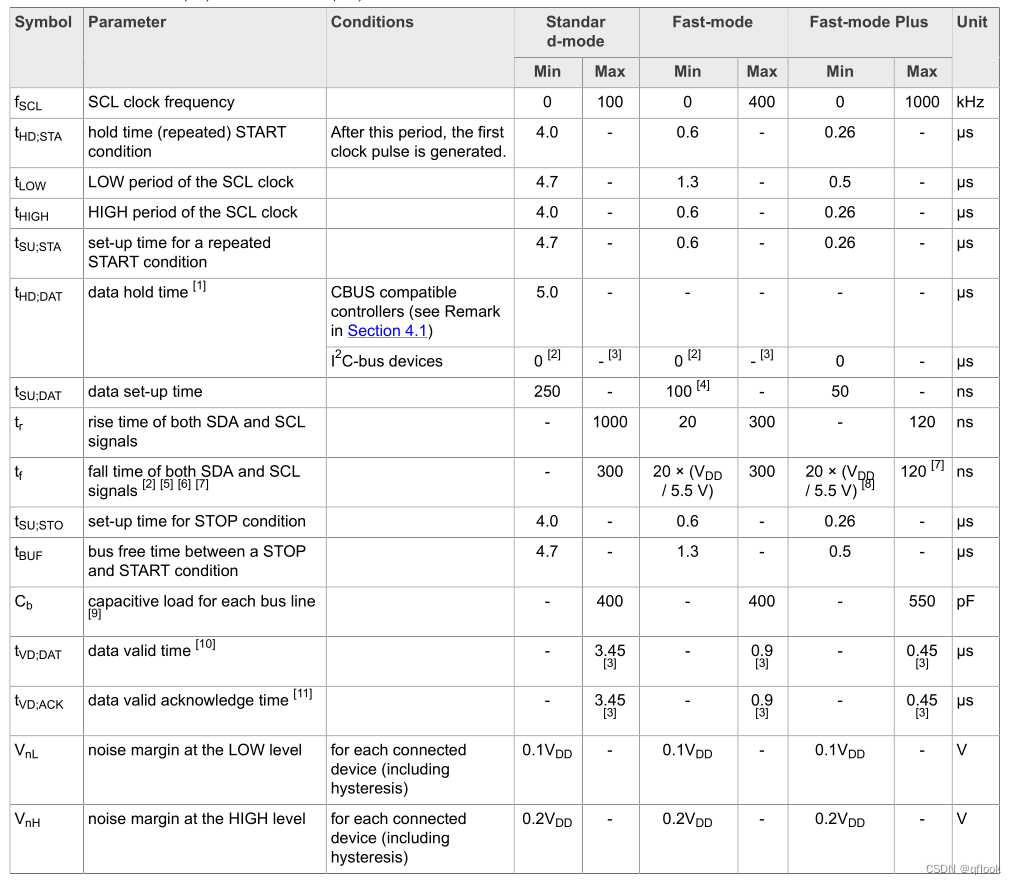

标准模式、快速模式和快速模式plus的时序参数要求如下:

3.高速模式时序要求

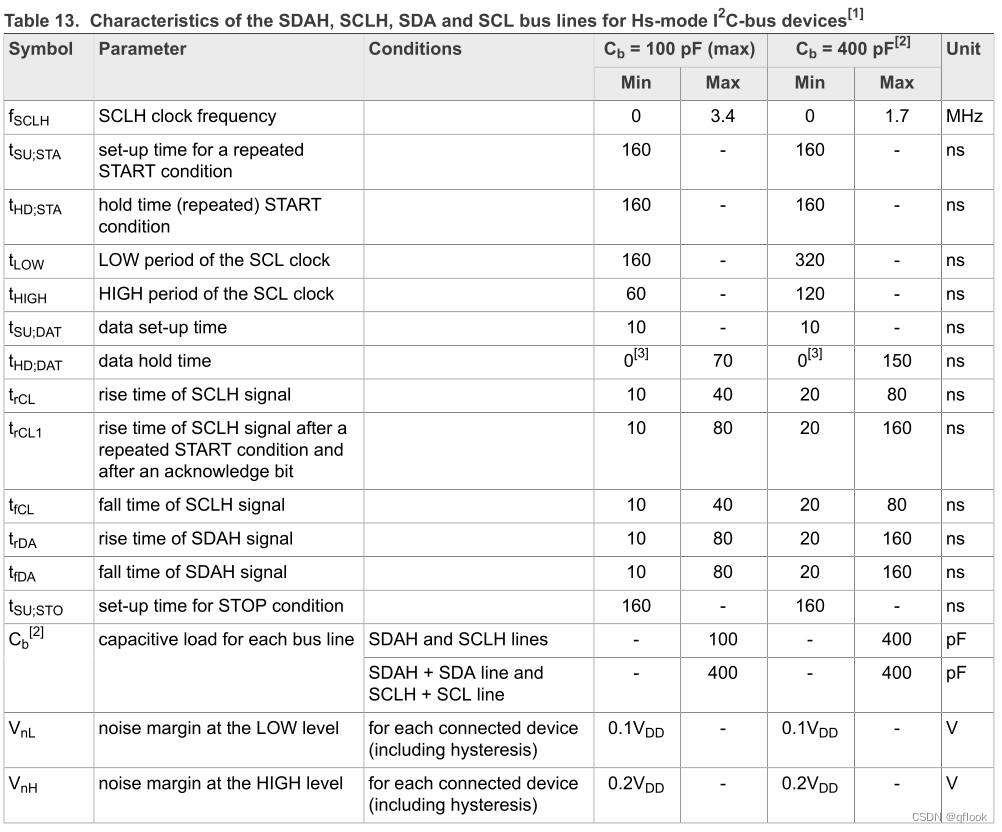

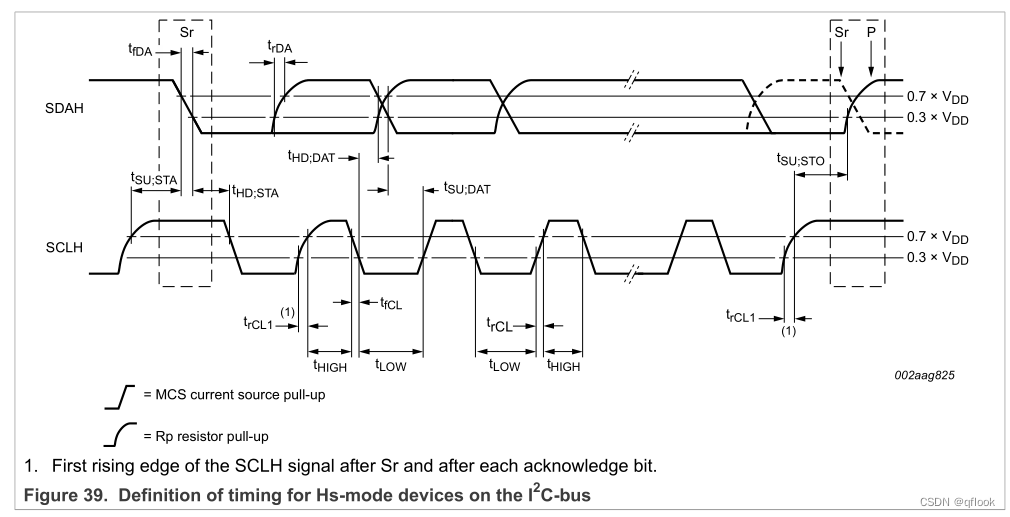

高速模式的时序参数要求,注意在不同负载电容下速率不同:

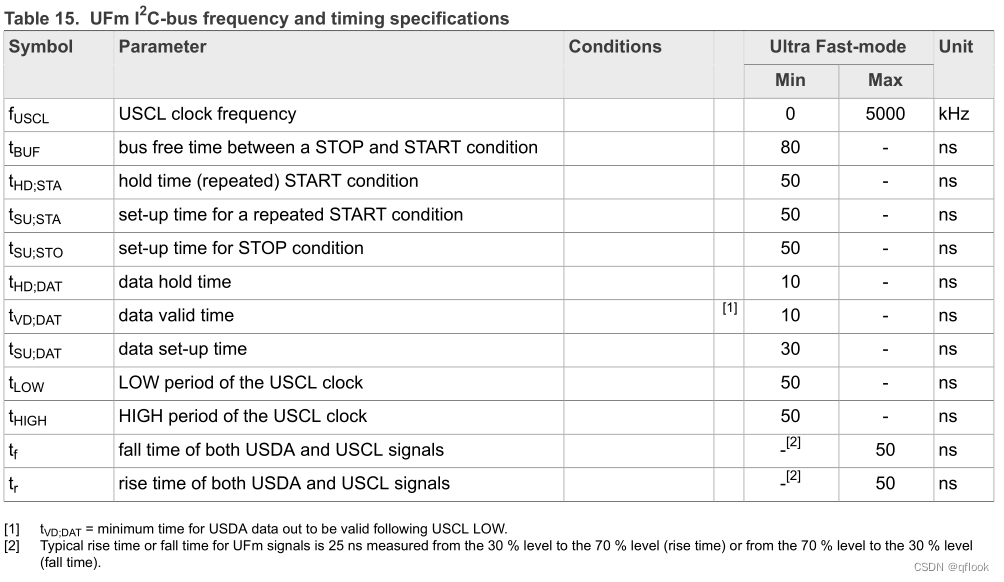

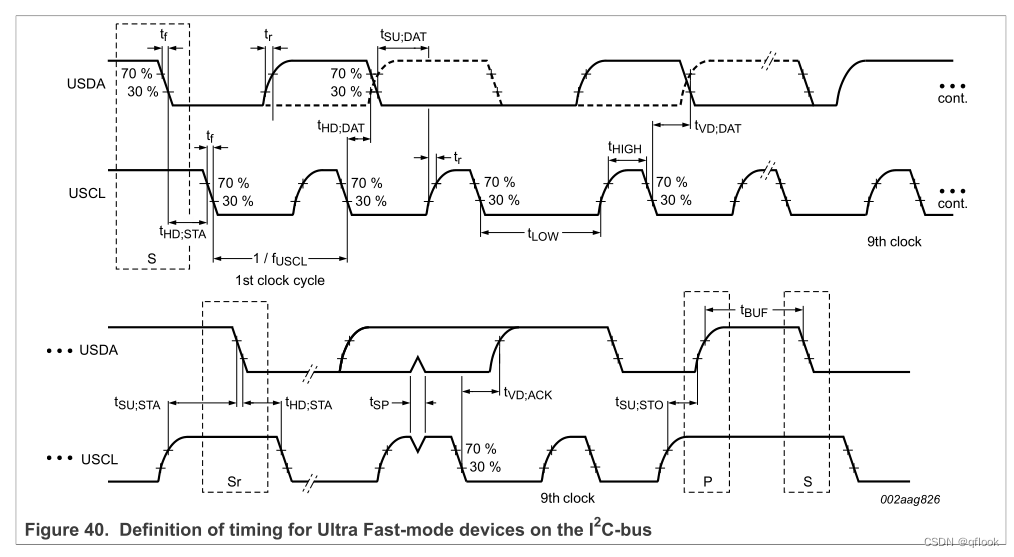

4.超快速模式时序要求

超快速模式的时序参数要求: