I2C Bus(Inter-Integrated Circuit Bus) 最早是由Philips半导体(现被NXP收购)开发的两线式串行总线,常用于微控制器与外设之间的连接。

一、概述

以下是 I2C 总线的一些特性:

- 只需要两条总线;一条串行数据线 (SDA) 和一条串行时钟线 (SCL)。

- 连接到总线的每个设备都可以通过唯一的地址进行寻址,并且始终存在简单的主/从关系;master可以作为主发送器或主接收器运行。

- 没有严格的波特率要求,例如 RS232,主机生成总线时钟

- 多主机总线,包括冲突检测和仲裁,以防止两个或多个主机同时启动数据传输时数据损坏。

- 串行、面向 8 位的双向数据传输在标准模式(standard mode)下最高可达 100 kbit/s,在快速模式(fast mode)下最高可达 400 kbit/s,在快速模式 Plus 下最高可达 1 Mbit/s ,或在高速模式(high-speed mode)下高达 3.4 Mbit/s。

- 在超快速模式下,面向 8 位的串行单向数据传输速度高达 5 Mbit/s。

- 片上滤波可抑制总线数据线上的尖峰信号,以保持数据完整性。

- 可连接到同一总线的IC 数量仅受最大总线电容的限制。 在某些条件下可能允许更大的电容。

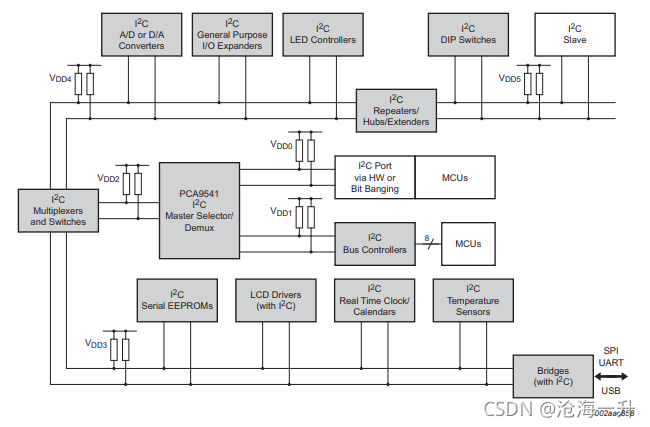

一个I2C应用如下:

二、I2C协议

1、标准模式与快速模式协议

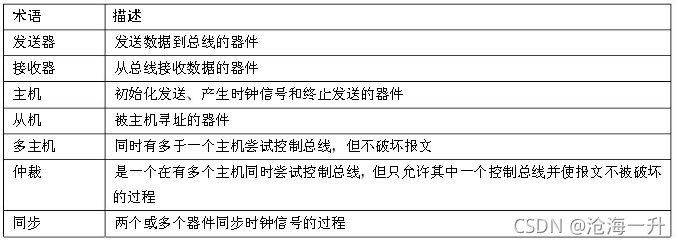

两线一一串行数据(SDA)和串行时钟(SCL)线在连接到总线的器件间传输信息。每个器件都有一个唯一的地址识别(无论是微控制器、LCD驱动器、存储器或键盘接囗),而且都可以作为一个发送器或接收器(由器件的功能决定),很明显,LCD驱动器只是一个接收器,而存储器则既可以接收又可以发送数。除了发送器和接收器外,器件在执行数据传输时也可以被看作是主机或从机,主机是初始化总线的数据传输并产生允许传输的时钟信号的器件,此时,任何被寻址的器件都被认为是从机。

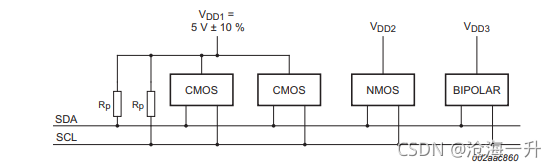

SDA和SCL都是双向线路,都通过一个电流源或上拉电阻连接到正的电源电压,当总线空

闲时,这两条线都是高电平。

连接到总线的器件输出级必须是漏极开路或集电极开路才能执行线与的功能。

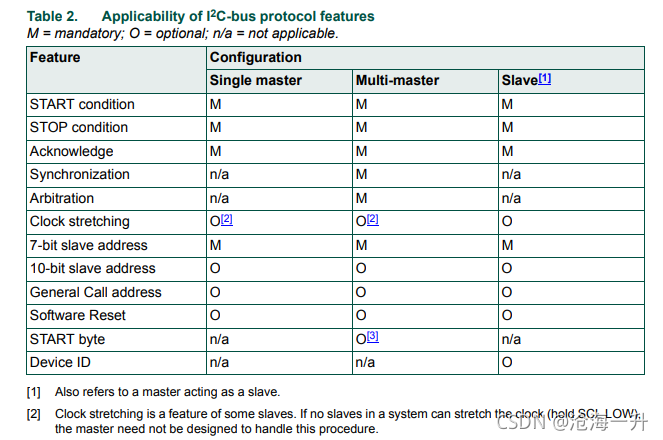

I2C 总线规范的强制要求和可选部分的使用以总结如下:

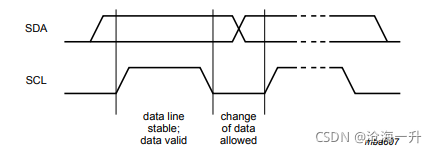

1) 数据有效性

在时钟的高电平期间(SCL为高),SDA 线上的数据必须是稳定的。 只有当 SCL 线上的时钟信号为 LOW 时,数据线的 HIGH 或 LOW 状态才能改变。 每一个时钟脉冲传输一个数据位。

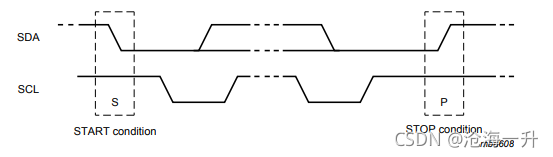

2)启动和停止条件

所有传输都以 START (S) 开始,并以 STOP (P) 结束。

- 启动条件:SCL为高电平时,SDA 线上的高电平到低电平转换。

- 停止条件:SCL为高电平时,SDA 线上的低电平到高电平转换。

START 和 STOP 条件始终由主机生成。 在 START 条件之后,总线被认为是忙碌的。 在 STOP 条件之后的某个时间,总线被认为再次空闲。

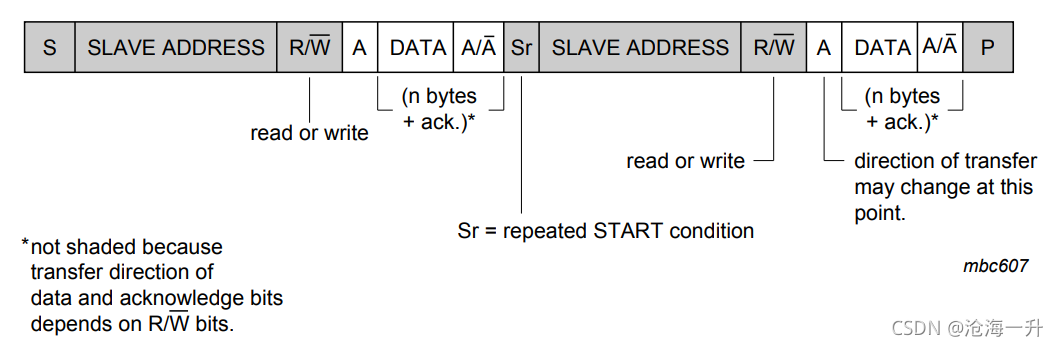

如果生成重复的 START (Sr) 而不是 STOP 条件,则总线保持忙碌。 在这方面,START (S) 和重复 START (Sr) 条件在功能上是相同的。

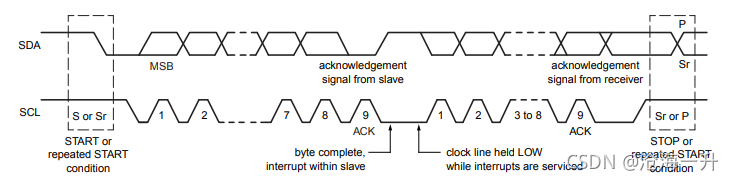

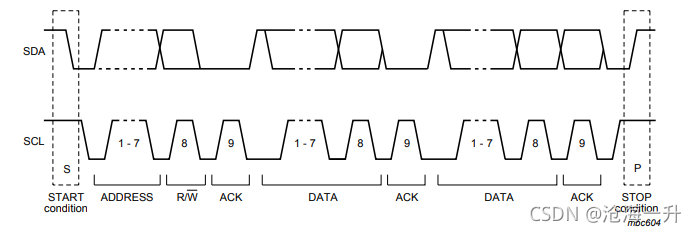

3)字节格式

SDA 线上的每个字节都必须是 8 位。 每次传输可传输的字节数不受限制。 每个字节后必须跟一个确认位(ack)。 数据首先以最高有效位 (MSB)传输。 如果从机在执行其他功能(例如服务内部中断)之前无法接收或发送另一个完整字节的数据,则它可以将时钟线 SCL 保持为低电平以强制主机进入等待状态。 当从设备准备好接收另一个字节的数据并释放时钟线 SCL 时,数据传输将继续。

4)确认位

确认位(ACK)在每个字节之后发送。确认位允许接收器通知发送器该字节已成功接收并且可以发送另一个字节。主机生成所有时钟脉冲,包括确认位的第九个时钟脉冲。

确认信号定义如下:发送器在确认时钟脉冲期间释放 SDA 线,因此接收器可以将 SDA 线拉低,并在该时钟脉冲的高电平期间保持稳定的低电平。还必须考虑建立和保持时间。

当 SDA 在第 9 个时钟脉冲期间保持高电平时,这被定义为未确认信号。然后,主机可以生成一个停止条件来中止传输,或者生成一个重复的 START 条件来开始新的传输。有五个条件会导致 未确认信号(NACK) 的产生:

- 发送地址的总线上没有接收器,因此没有设备响应确认。

- 接收器无法接收或发送,因为它正在执行一些实时功能,还没有准备好开始与主设备的通信。

- 在传输过程中,接收方得到了它不理解的数据或命令。

- 在传输过程中,接收方不能再接收任何数据字节。

- 主接收器必须向从发送器发出传输结束信号。

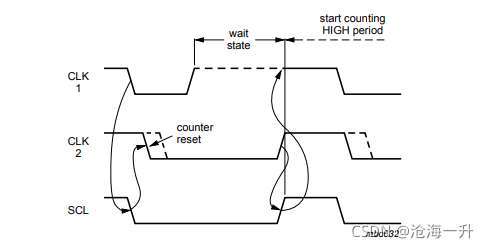

5)时钟同步

两个主机可以同时在空闲总线上开始传输,并且必须有一种方法来决定哪一个控制总线并完成其传输。 这是通过时钟同步和仲裁完成的。

在单主系统中,不需要时钟同步和仲裁。

使用 I2C 接口与 SCL 线的线与连接来执行时钟同步。

这意味着 SCL 线上的高电平到低电平转换会导致相关主设备开始对它们的低电平周期进行计数,并且一旦主时钟变为低电平,它就会将 SCL 线保持在该状态,直到达到时钟高电平状态。 但是,如果另一个时钟仍在其低电平周期内,则该时钟从低电平到高电平的转换可能不会改变 SCL 线的状态。 因此,SCL 线由具有最长低电平周期的主机保持低电平。 具有较短低电平周期的主机在此期间进入 高电平的等待状态。

当所有相关的主机都计完它们的低电平周期时,时钟线被释放并变为高电平。 这样主时钟和 SCL 线的状态之间就没有区别了,所有的主时钟开始计数它们的高电平周期。 第一个完成其高电平周期的主机再次将 SCL 线拉低。 这样,一个同步的SCL时钟就产生了,它的低电平周期由时钟低电平周期最长的主机决定,高电平周期由时钟高电平周期最短的主机决定。

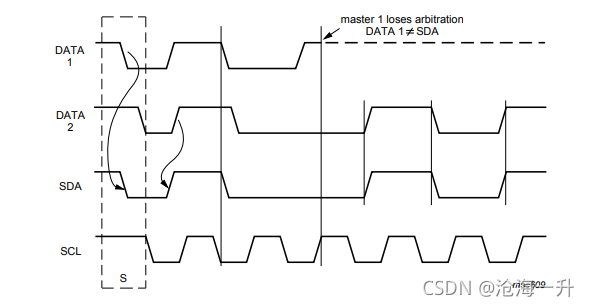

6)仲裁

仲裁与同步一样,是指仅当系统中使用多个主设备时才需要的协议的一部分。从设备不参与仲裁程序。 只有当总线空闲时,主机才可以开始传输。

两个主设备可以在 START 条件的最小保持时间内生成一个 START 条件,从而在总线上产生一个有效的 START 条件。然后需要仲裁来确定哪个主机将完成其传输。

仲裁是一位一位进行的。在每一位进行传输期间,当 SCL 为高电平时,每个主机都会检查 SDA 电平是否与其发送的电平相匹配。这个过程可能需要很多位。只要传输相同,两个主机实际上可以无误地完成整个事务。第一次主机尝试发送高电平,但检测到 SDA 电平为低电平时,主机知道它已失去仲裁并关闭其 SDA 输出驱动器。另一个主节点继续完成其事务。在仲裁过程中不会丢失任何信息。失去仲裁的主机可以生成时钟脉冲,直到失去仲裁的字节结束,并且必须在总线空闲时重新开始其事务。如果主机还包含从机功能并且在寻址阶段失去仲裁,则获胜的主机可能正在尝试对其进行寻址。因此,丢失的主设备必须立即切换到其从设备模式。

由于 I2C 总线的控制完全取决于竞争主机发送的地址和数据,因此没有中央主机,也没有总线上的任何优先级顺序。

7)读写控制

在 START 条件 (S) 之后,发送从地址。 该地址有 7 位长,后跟第 8 位,即数据方向位 (R/W)——“0”表示传输 (WRITE),“1”表示请求数据 (READ)。

数据传输总是由主机产生的停止条件 (P) 终止。 但是,如果主机仍然希望在总线上进行通信,它可以生成重复的 START 条件 (Sr) 并寻址另一个从机,而无需首先生成 STOP 条件。 在这样的传输中,读/写格式的各种组合都是可能的。

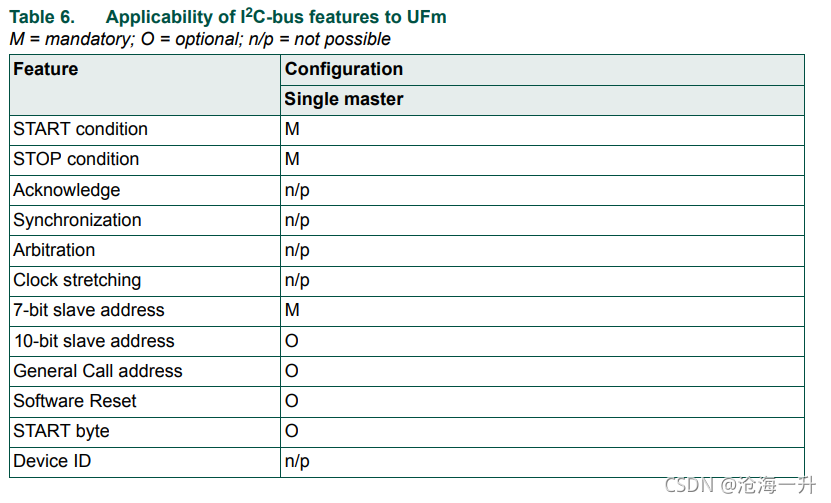

2、 Ultra Fast-mode 协议

UFm(Ultra Fast-mode) I2C 总线是一种 2 线串行总线,可在高至 5 MHz 的频率范围内单向传输数据。当速度大于 1 MHz 时,驱动 LED 控制器和其他不需要反馈的设备最为有用。

UFm I2C 总线协议基于标准 I2C 总线协议,该协议由 START、从地址、命令位、第九个时钟和一个停止位组成。命令位仅为“写”,第 9 个时钟上的数据位被驱动为高电平,由于总线的单向特性而忽略 ACK 周期。

2 线驱动器由 UFm 串行时钟 (USCL) 和串行数据 (USDA) 组成。从设备包含一个唯一地址(无论是微控制器、LCD 驱动器、LED 控制器还是 GPO)并且仅作为接收器运行。 LED驱动器可能只是一个接收器,UFm可以支持,而存储器可以接收和传输数据,UFm不支持。 UFm I2C 总线也不支持多主机功能。在 UFm 中,主机是唯一在总线上启动数据传输并生成时钟信号以允许传输的设备。寻址的所有其他设备都被视为从设备。

其规范要求如下:

USDA和USCL都是单向线路,当总线空闲时,两条线都被输出级的上晶体管拉高。其基本传输条件与标准模式一致。