1 PDN概念

电源完整性的仿真,实际上是在仿真以及优化系统中的等效串联电阻。知道了仿真以及优化的目标之后,接下来就是要弄明白这个串联电阻从哪儿来以及怎么优化。

整个系统中的串联电阻实际上由三部分组成:没有相位的阻抗,有相位的容抗和感抗,得益于相位,在某个特定的频点,容抗和感抗会大小相等,相位相反而相互抵消,这时候整个系统中就剩下了阻抗,所以整个系统的串联电阻达到了一个最低值,这种现象就是----谐振。当系统处于谐振点时候,整个系统会有一个最小的串联电阻,所以第一个优化电阻的手段就是让谐振来的更频繁一点。 可以看到电阻是一个频率相关的变量,除去谐振点这种特殊的频率,总的来说随着频率的升高,阻抗恒定不变,感抗升高,容抗降低。所以我们找到了第二个优化回路电阻的方法,对于高频来说,我们在优化串联电阻的时候,实际上是在想办法减小回路电感。

PDN重要性:

提供负载的工作电源提供稳定的参考电平

电源噪声大带来的危害:

信号抖动增大

信号噪声裕量减小

电路功能故障

EMI超标

PDN设计要求:

PDN满足负载对电源电压的要求(控制压降)

PDN满足负载对电源电流的要求(控制温升)

确定动态电流和目标阻抗

选用合适的电源芯片或者电源模块

根据目标阻抗设计电源去耦网络

确定去耦电容规格

量化去耦电容数量

去耦电容摆放

信号参考平面的PDN要求低阻抗

没有目标阻抗要求或目标阻抗偏高的PDN不适合作为高速信号的参考平面

PDN载流能力及压降

电源通道上的最大负载

负载上容许的压降

PCB容许的温升:单板容许温升上限 5—25度

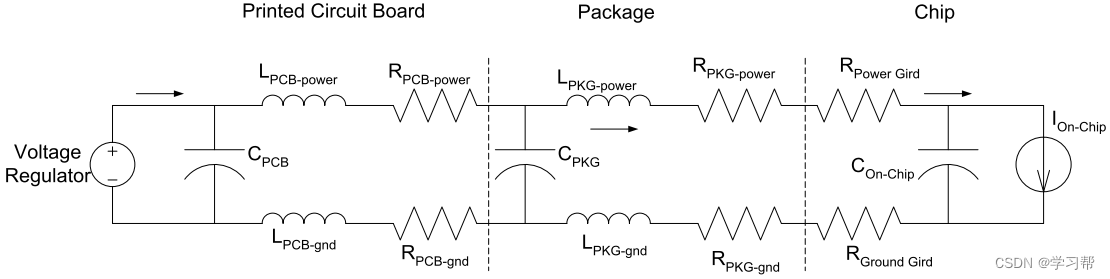

VRM(常见DCDC或者LDO)模块对负载电压的检测及调整输出都需要时间,通常在毫秒(ms)级。当稳压模块无法及时响应负载对电流需求的快速变化时,稳压电源的输出就会下降,从而产生电源纹波。通常VRM不能对变化时间低于100ms的瞬态涌流变化做出响应,即VRM纹波噪声是KHz级别的。低于100ms的瞬态噪声需要借助电源分配系统(PDS)其他模块如去耦电容、电源地平面、片上去耦加以滤波。

评价VRM性能的一个重要指标就是小信号输出阻抗,好的VRM设计可以在负载电流允许的整个范围内得到电压纹波很小的输出电压,即负载电流变化,小信号输出阻抗变化不大。但是随着频率升高,回路增益下降, VRM输出阻抗增加,因此需要在VRM附近并联几个大容值电容来降低VRM的输出阻抗。

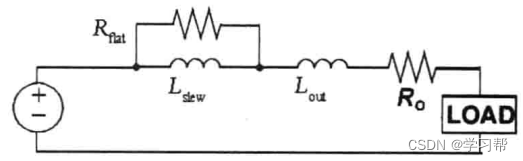

典型的4元件VRM电路模型

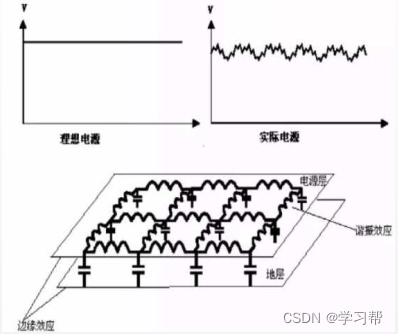

PCB电源地平面形成平板电容器,电源和地平面噪声经过平板电容,不同边界的多重反射构成了在PCB中常见的谐振现象。电源、地平面的谐振特性对我们系统的性能带来不利的影响。

在谐振频率附近,能量会被介质存储或消耗掉,而且只要该电源、地平面的位置有激励源,就很容易起振。通过增加滤波电容或适当调整芯片的外置,从而达到我们的设计要求。一般FR4板材, Er较小,平板电容值太小了,对电源滤波起不到明显作用。电源和地平面的实际作用就是为芯片和去耦电容间提供低电感路径。

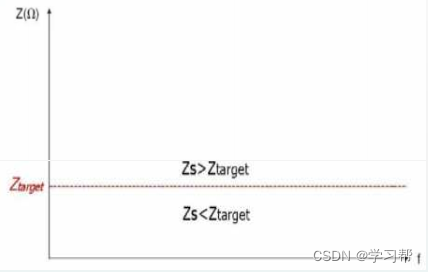

从阻抗算式 Z=ESR+jwESL+1/(jwC) 来看, 目标阻抗与工作频率密切相关。

选择适当的电容对实现目标阻抗至关重要,由于电容的材料和结构等不同,不同种类的电容具有不同的频率特性。一般地, 1kHz~1MHz频段选用电解电容, 1MHz~100MHz频段选用高频陶瓷电容。在100MHz以后,平面层地滤波作用逐渐突出,到GHz频段,平面层成为主要地电源滤波元件。

在高速电路的设计中,为了保证IC等器件从直流到时钟频率的多次谐波频段上都能稳定工作,从IC等器件向电源传输系统看进去的阻抗必须保持在较低的值。这就是目标阻抗,目标阻抗是我们所期望的电阻值Ztarget, Ztarget与一定的频率范围相关。Ztarget,的计算方法:

Power Supply Voltage是工作电压

Allowed Ripple 是允许的工作电压纹波系数

Current 是工作电流

对电源、地平面的分析,有效的手段是采用目标阻抗控制来实现对电源分配系统电源噪声的

控制,也即将每个芯片的电源、地管脚附近作为观测端口,控制端口的输入阻抗在一定的频率范围内,达到芯片可以接受的容限值,从而控制⊿ I噪声。但是对电源、地平面的分析,涉及到物理结构、物理位置、叠板、滤波、各个器件的动态工作特性等等,非常复杂,详细准确的分析需要采用2.5D电磁场法进行有限元计算,并结合电路仿真的手段,将二者融合。

2 PDN仿真步骤

A) AC simulation:

Use accurate stack-up information with permittivity and loss tangent.

Enable only PDN nets and classifies PDN VDD nets as PowerNets and GND as GroundNets

Disable “Keep shape enabled when net is disabled”

Set special voids to 0.1 mm for all four types of special void.

Set mesh edge length to 1 mm.

Turn off via fanning.

Run shape processing.

Simulate each domain separately for large power domain.

B) DC simulation:

Set VRM at sense point for switching mode power supply (SMPS)

Set VRM at PMIC output for low dropout regulator(LDO)

3 PDN仿真设置(AC)

3.1 文件转换

以pads asc文件为例

-

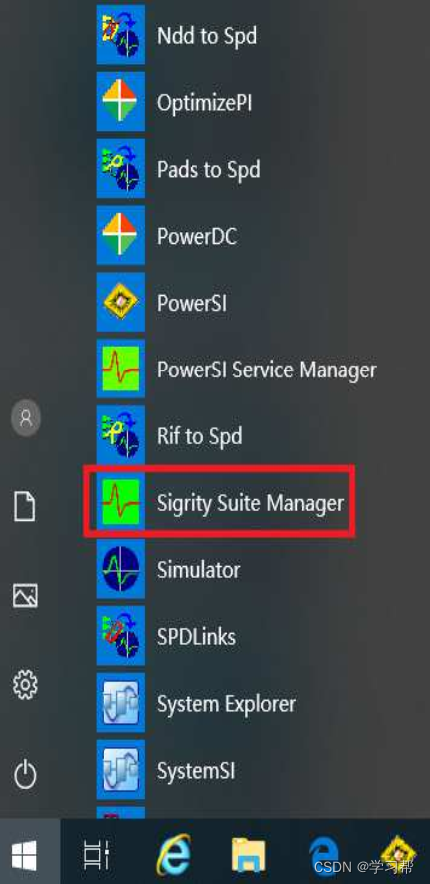

选择sigrity suite manager

-

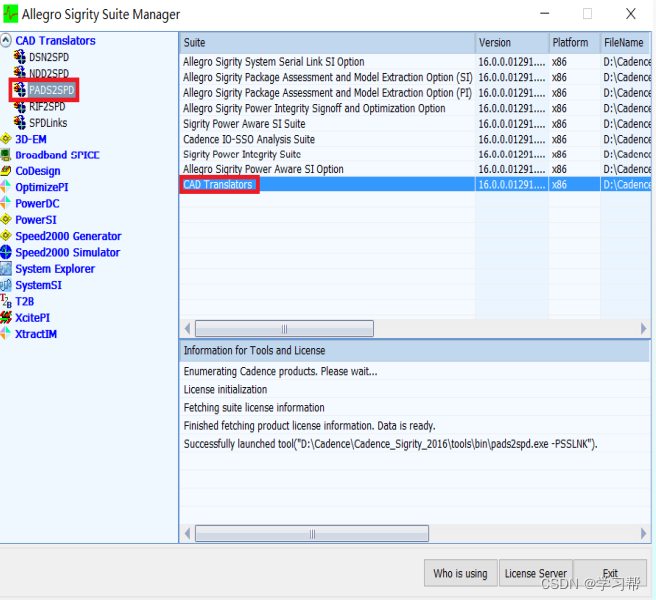

打开allegro sigrity suite manager,选择PADS2SPD->CAD Translators

-

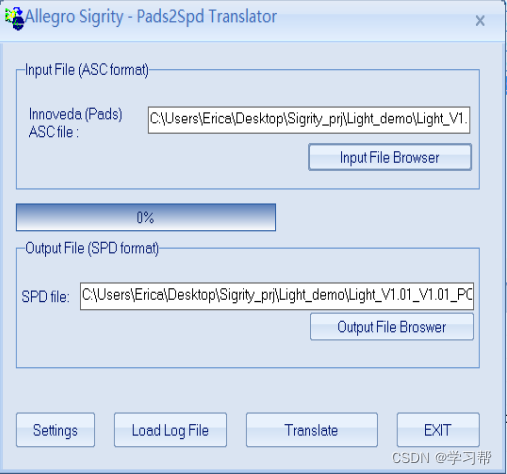

双击CAD Translators ,打开Allegro Sigrity Pads2Spd Translator将PCB文件转换成Sigrity专用的仿真文件格式SPD文件

3.2 启动Power SI软件

双击图标,进入Power SI主界面,选择Model Extraction仿真模式,接下来导入仿真文件,进行