1 DFT

1.1 DFT类型

1、扫描链(SCAN):

扫描路径法是一种针对时序电路芯片的DFT方案.其基本原理是时序电路可以模型化为一个组合电路网络和带触发器(Flip-Flop,简称FF)的时序电路网络的反馈。

Scan 包括两个步骤,scan replacement和scan stitching,目的是把一个不容易测试的时序电路变成容易测试的组合电路。

2、内建自测试(BIST):

内建自测试(BIST)设计技术通过在芯片的设计中加入一些额外的自测试电路,测试时只需要从外部施加必要的控制信号,通过运行内建的自测试硬件和软件,检查被测电路的缺陷或故障。和扫描设计不同的是,内建自测试的测试向量一般是内部生成的,而不是外部输入的。内建自测试可以简化测试步骤,而且无需昂贵的测试仪器和设备(如ATE设备),但它增加了芯片设计的复杂性。

3、JTAG:

JTAG(Joint Test Action Group,联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试.

JTAG的基本原理是在器件内部定义一个TAP(Test Access Port,测试访问口)通过专用的JTAG测试工具对内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试.

4、ATPG:

ATPG(Automatic Test Pattern Generation)自动测试向量生成是在半导体电器测试中使用的测试图形向量由程序自动生成的过程。测试向量按顺序地加载到器件的输入脚上,输出的信号被收集并与预算好的测试向量相比较从而判断测试的结果。

1.2 扫描链脚本

#############################

# set library

#############################

set search_path [concat $search_path ./lib]

set target_library {your_lib.db}

set link_library {* your_lib.db}

set symbol_library {your_lib.sdb}

set physical_library {your_lib.pdb}

#############################

# read design file

#############################

read_verilog ./src/*.v

current_design top

link

uniquify

check_design

#############################

# set load and constraints

#############################

# load_constraints

# timing_constraints

check_timing

#############################

# basic synthesis

#############################

compile

write -format verilog -hier -output ./output/top_netlist.v

#############################

# dft configuration

#############################

set hdlin_enable_rtldrc_info true

set_scan_configuration -style multiplexed_flip_flop

source ./dft/top.tmv

compile -scan

write -format verilog -hier -output ./output/top_netlist_dft.v

# remove_design top

# read_verilog ./output/top_netlist_dft.v

# current_design top

source ./dft/circuit.tp

dft_drc

insert_dft

write -format verilog -hier -output ./output/top_scan.vg

write_test_protocol -output ./output/top.spf

top.tmv内容:

#set test timing variables

set test_default_delay 0

set test_default_bidir_delay 0

set test_default_strobe 40

set test_default_period 100

top.tp内容:

set_dft_signal -view existing_dft -type ScanClock -timing {45 55} -port clk

set_dft_signal -view existing_dft -type Reset -active_state 0 -port rst_n

create_test_protocol

1.3 DFT前后对比

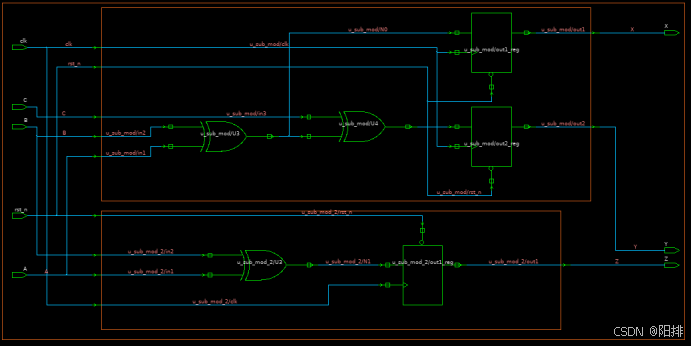

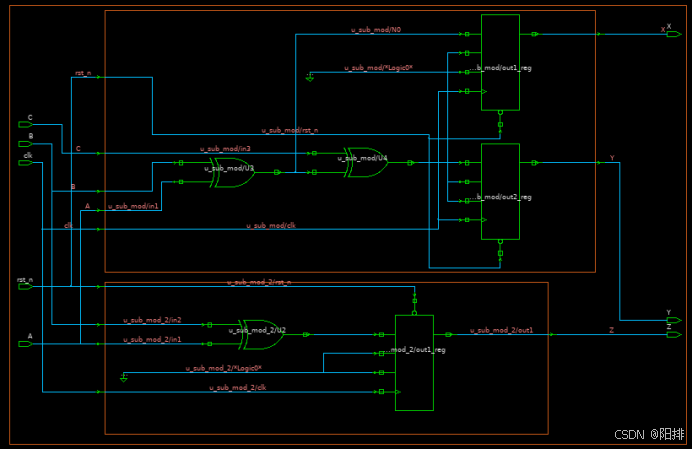

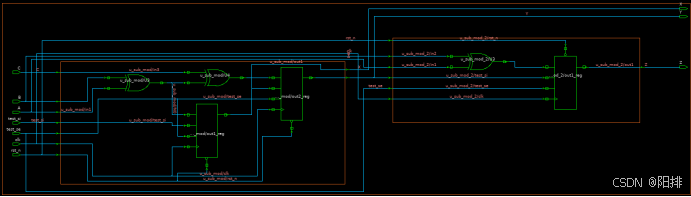

1、原始设计文件top_netlist.v:

2、加入DFT,使用compile -scan后的设计文件top_netlist_dft.v:可以看到普通的DFF已经变成了带MUX的DFF,不过扫描链的控制引脚依然是全部拉低。

3、insert_dft之后的设计文件top_scan.vg:扫描链的控制引脚接到外部,输出引脚也已经引出。

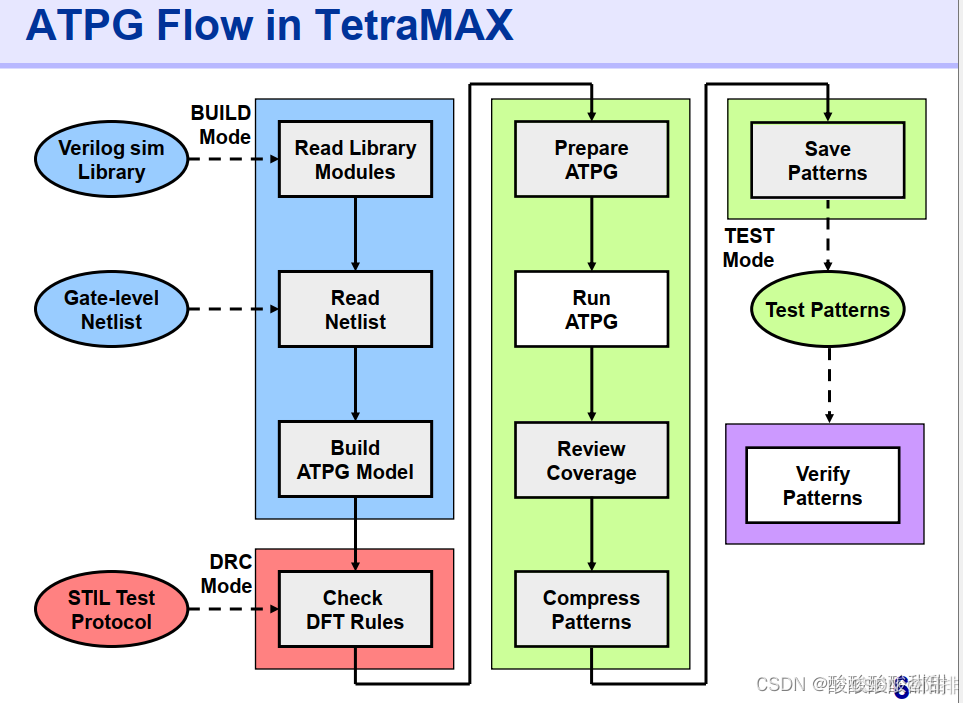

2 TetraMax

2.1 启动tmax

找到TetraMax安装路径,终端输入:

<software_path>/tmax2

tmax2比tmax性能更好。

2.2 ATPG脚本

set_messages -log ./dft/tmax/tmax2_log.txt -replace

# Read library and design with dft

read_netlist -library ./lib/tsmc090.v

read_netlist ./output/top_scan.vg

# Build the ATPG Model

run_build_model top

# Set up and run DRC

set_drc ./output/top.spf

run_drc

# Add faults and run ATPG

add_faults -all

write_faults ./dft/tmax/all_faults.txt -replace -all

run_atpg

# Write the patterns to store challenge sequences and ideal response sequences

write_patterns ./dft/tmax/top_patterns.stil -form stil

参考文献

https://zhuanlan.zhihu.com/p/159273941

https://blog.csdn.net/ciscomonkey/article/details/109151105

https://blog.csdn.net/Cloudriver_/article/details/134210464

https://blog.csdn.net/qq_43858116/article/details/131630503