前言

本文主要内容是对环路滤波器 模块设计设计进行阐述,LPF在电荷泵频率综合器中,主要作用是进行滤波,消除毛刺,因此一个简单的RC就可以起到很好的效果。本文主要目的是为了补充【模拟集成电路】频率综合器(Frequency Synthesizer,FS)设计 中的设计内容。更高性能的LPF,如果有必要,后续更新(私信我)

环路滤波器设计

(一个错误的例子)

如果不考虑环路稳定性,只考虑所谓的纹波或者取平均。一个LPF结构如下,但实际上这个结构是很难稳定的(详细的有时间再补充),如果会PLL的一眼就能看出来普通的RC实际上并不可取(至少这个不太行)

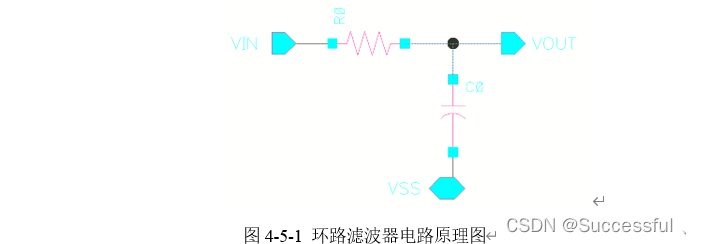

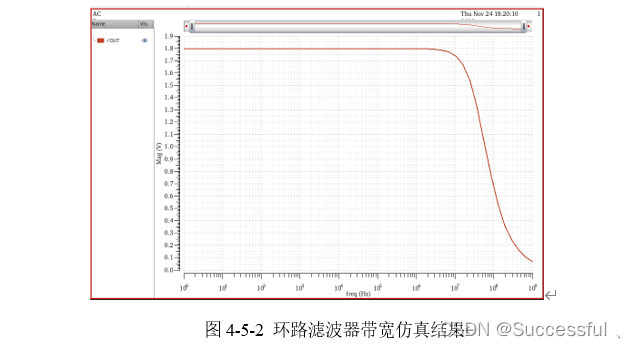

在电荷泵锁相环频率综合器中,环路滤波器的作用是将电荷泵输出的脉冲电流信号转换为较为平稳的压控振荡器的控制电压信号。整个过程中环路滤波器既起到信号转换作用又起到滤波作用。由于锁相环是一个典型的闭环负反馈系统,系统稳定性以及动态特性尤为重要,而环路滤波器的参数设计恰恰决定了整个锁相环的稳定性和动态特性。为了保证锁相环能够迅速锁定,就要求当电荷泵输出电流为零时,压控振荡器的输出频率仍有可能发生改变,那么环路滤波器在直流分量时就要有无穷大的增益。一个电阻串联一个电容可以在直流频率分量是提供一个无穷大的阻抗,电流到电压的增益即为无穷大,同时其提供了一个零点有助于改善整个环路的相位裕度,从而改善稳定性。压控振荡器的电压控制线越稳定,则压控振荡器的相位噪声越好,输出信号的频谱就越纯净。本文中环路滤波器的实现电路以及仿真结果分别如图4-5-1、4-5-2所示。

仿真结果

| 分割线 |

各部分链接链接:

频率综合器(Frequency Synthesizer,FS)设计 链接:【模拟集成电路】频率综合器(Frequency Synthesizer,FS)设计

鉴频鉴相器(PFD)设计 链接:【模拟集成电路】鉴频鉴相器设计(Phase Frequency Detector,PFD)

电荷泵(CP)设计 链接:【模拟集成电路】电荷泵(CP)设计

压控振荡器(VCO)设计 链接:【模拟集成电路】宽摆幅压控振荡器(VCO)设计

分频器(DIV_TSPC)设计 链接:【模拟集成电路】分频器(DIV_TSPC)设计