前言

在工程设计中,我们往往会遇到需要跨时钟域的设计,除了需要做好时钟同步之外,跨时钟域约束也是必不可少的,否则就会遇到工程能编译通过,但是时序报告会有报红警告的问题,这对工程设计来讲是一个不小的隐患。下面将我常用的跨时钟域约束小技巧分享给大家。

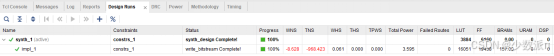

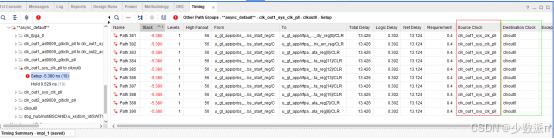

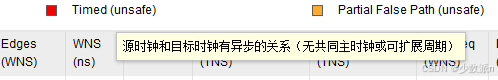

当我们没有做好跨时钟域处理,但是程序又成功编译通过后就会出现下面这种时序报警的问题。

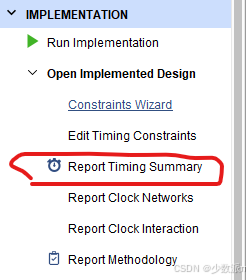

此时我们可以通过Report Timing Summary打开时序报告查看具体信息。

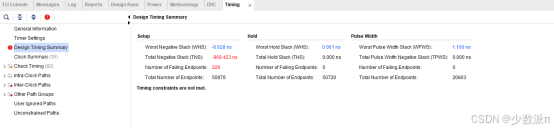

在时序报告中我们可以看到,最差的建立时间余量(WNS)为-8.628ns,总的负建立时间余量之和(TNS):-968.423ns,这两个是我们要关注的重点。

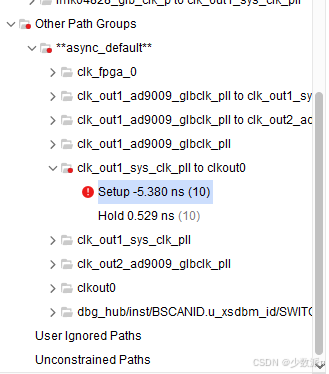

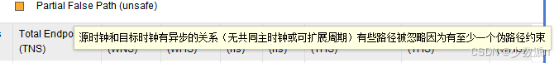

此时我们可以根据右侧目录指引找到具体报警告的时序路径。

如下图中的报告显示,其中红色框中为源时钟,绿色框中为目的时钟,此时我们已经可以对跨时钟域进行约束,但这里并不是最全面的跨时钟域报告,我们接着往下看

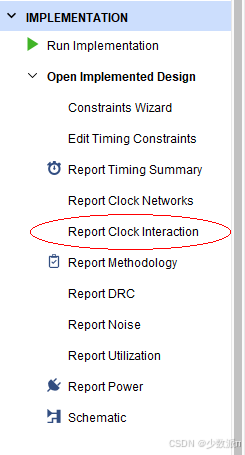

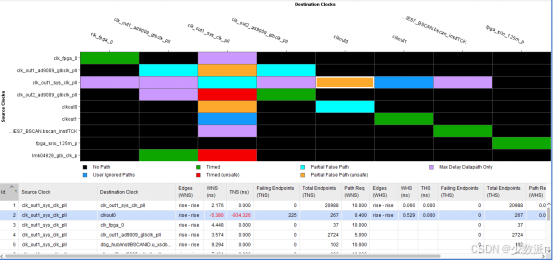

我们点击左侧Repot Clock Interaction打开跨时钟域报告

在弹出的框中点击ok

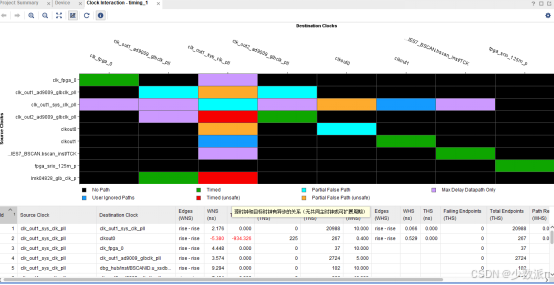

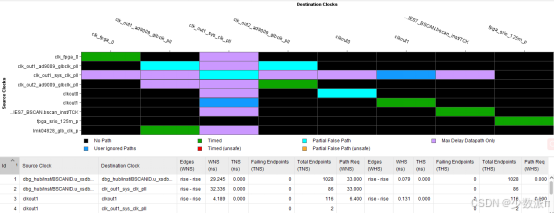

此时给我们打开了一个很直观的时序框图,其中,左侧为源时钟,上方为目的时钟,我们需要重点关注橙色和红色色块,这两种就是需要我们做跨时钟域处理的时钟

在这里我们可以点击色块,会在下面指出对应的时序路径

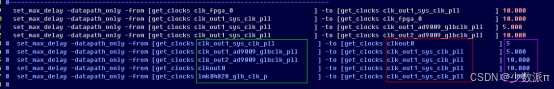

跨时钟域约束的格式如下:X:源时钟;Y:目的时钟;T:约束时钟周期。这里的约束时钟周期推荐使用源时钟和目的时钟中频率高周期小的时钟周期作为约束时钟周期。

set_max_delay -datapath_only -from [get_clocks xxxxxx ] -to [get_clocks yyyyyy ] ttt

下面我们需要约束的跨时钟域路径按照格式约束在xdc文件当中后重新编译

编译完成后再次打开时序报考和跨时钟域报考发现之前的时序警告和跨时钟域中的红色和橙色色块都消失了。现在的时序已经完全满足设计要求了。

有用记得收藏点赞哦!