关于PCIE非透明桥 cache一致性

PCIE非透明桥提供了两种机制来从local node往remote node迁移数据,分别是基于地址映射和内嵌的

DMA。对remote节点而言,当它接受数据的时候,CPU可能是不知情的,因此需要保证cache一致性;

对local节点,当通过DMA往它自己的内存传输数据时,本地的CPU也不会被通知,因此需要考虑cache

一致性。

不同的平台实现Cache一致性的机制不一样,ARM平台需要软件参与,而IntelX86平台硬件能够自动维

护cache一致性。x86提供了不同的cache一致性的级别,一些特殊的应用可能需要定制化的cache一致

性管理策略。

1. Intel X86 cache一致性级别

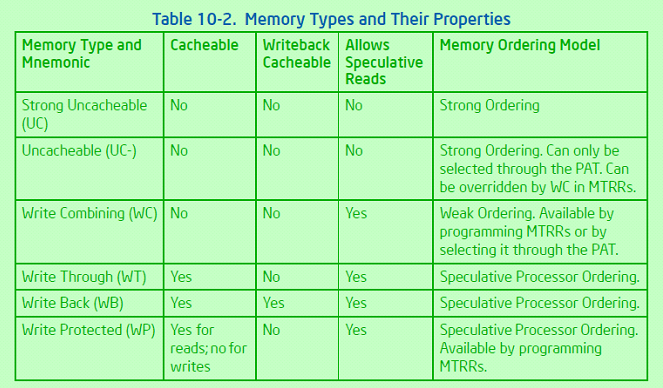

Intel根据不同的应用需求定义了不同的一致性级别:

2. Intel X86 cache管理的三种级别

Intel提供了不同粒度来管理Cache一致性:处理器核内的CR0寄存器的CD/NW位:使能或禁止整个系统的cache;

CR3的PCD/PWT bit和页表和页目录表项的PCD/PWT属性位:分别控制所有的页表、某个具体的页/页表的cache属性;

MTRR ( Memory Type Rang Register): 指定某段范围的地址是cache的还是uncache的

3. cache一致性与DMA

DMA buffer 和 DMA memory

DMB Buffer: 是物理内存的一部分,存放从DMA接受到的数据,或者要发送到DMA的数据

DMA memory:物理外设上的一段存储空间,比如显卡上的独立显存,或者IO空间、PCI memory 空间

coherence DMA 和 streaming DMA

DMA的功能是在DMA buffer和DMA memory 之间搬运数据,一致性的要求是保证:当需要读从DMA

接受到的数据时,看到的是最新的数据;而往DMA写的时,待发送给DMA的数据也一定是最新的。

coherence DMA: 如果DMA buffer对应的物理内存连续,由连续的物理页组成,只要一次DMA传输的

数据长度允许,DMA一次操作就能够往这些连续的物理页传完数据。它的好处是快,不足的是需要寻找

到连续的物理内存页块。除此之外,它好要求保证cache一致性。内核提供的dma_malloc_coherence()

函数能够做到这两点,对x86而言,由于硬件上已经保证了DMA buffer的cache一致性,只需要找到物

理地址连续的页块就好。如果硬件不能保证cache一致性,要求这些物理地址都是uncached的。

streaming DMA: 如果DMA buffer对应的虚拟地址连续,但不确定物理地址是否连续,受DMA的一个

描述符对物理地址连续的要求,需要找到虚拟地址对应的所有物理页框,逐一用DMA进行传输。它的好

处是对地址没有限制,驱动和内核屏蔽了拆分物理页框的细节,随叫随传。这种模式下对cache一致性的

保护是取决于传输方向:

从内存到DMA :要把每个页框对应的cache的东西写回到内存

从DMA到内存:要把每个页框对应的cache无效,保证后面的访问指向内存

对X86而言,硬件已经实现了管理cache一致性的机制,上面的cache写回和无效的工作不需要。

4. PCIE非透明桥cache一致性的考虑

不考虑特殊的情况下,根据上面的分析,在利用DMA进行数据传输的情况下,local DMA buffer 的

cache一致性总能得到保证,由于PCIE非透明桥非透明桥的地址转换功能,在实际的应用场景下,local

DMA memroy其实映射到了remote 节点的local DMA buffer,因此它的cache一致性也得到x86硬件

的保护。当然如果考虑到PCIE非透明桥对非易失性存储的支持,针对防止数据丢失的要求,除了保证

cache一致性外,还要求:

所有的写访问直接去往内存;

所有的读也来自内存(在考虑性能的前提下,允许读来自cache)

参考资料:

1.Intel,IA32_Dev_3A.pdf

2.陈学松,《深入Linux内核设备驱动机制》

转载于:https://blog.51cto.com/xiamachao/1721990