这里写自定义目录标题

前言

本文介绍PCIe以及PCI的一些小知识点

什么是PCIe

PCI

PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,它是目前个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽

PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种

PCI是一种并行总线

PCI的局限

从图中就能看出PCI总线频率不高,且随着带宽的增加负载能力迅速减少。

即使PCI-扩展也存在这样的特征。

PCIe

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准

PCIe是一种串行总线

物理链路

PCIe 链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和

RX(接收逻辑)

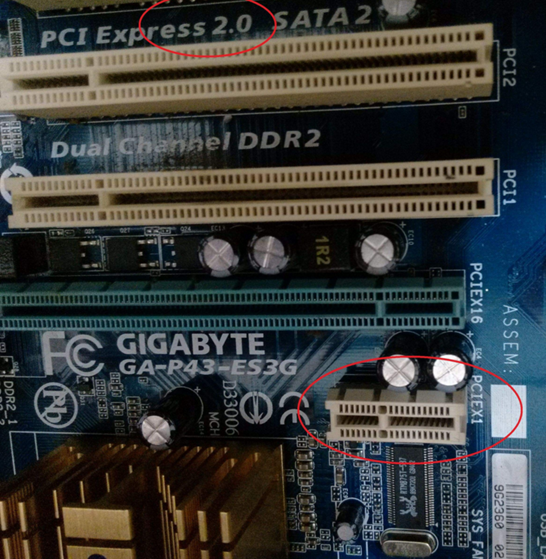

接口

计算规则:

比如当前的PCIe版本是2.0 X4

GT/s —— Giga transation per second (千兆传输/秒)我的理解为单位,在这里体现的是bit,注意编码方案8b/10b 指没发送1个直接需要发送10个bit。即有效带宽为0.8

注意这个进位是按1000算的

那么每一条line 吞吐量(带宽) == 5Gbit/s / 8 * 0.8 =500 MB/s 那么X4就是2GB/s

PCIe的一般应用

PCIe一般应用在数据量大 吞吐量大的场景,比如视频的传输、码流的传输

专业名词

域

- PCI 设备具有独立的地址空间,即PCI 总线地址空间,该空间与存储器地址空间通过HOST主桥隔离

- pcie设备使用的都是pcie域中的地址,而cpu侧使用的是存储器域地址,二者不能混用,必须要经过HOST主桥进行地址转换方可访问

Host主桥

主要功能是隔离处理器系统的存储器域与处理器系

统的PCI 总线域,管理PCI 总线域,并完成处理器与PCI 设备间的数据交换

RC和EP

-

Root Complex:

一个系统元素,可在一个芯片内也可不在一个芯片内

Host Bridge,PCIe控制器,… -

End Point:

Pcie设备

配置空间

PCIe设备分PCIe设备以及PCIe桥

Type0 普通设备比如PCIe接口网卡设备、串口设备

Type1 是一个桥设备,用于扩展PCIe接口,因为PCIe是点对点的设备所以扩展需要桥

Vendor ID 代表PCI 设备的生产厂商,

Device ID 代表这个厂商所生产的具体设备。

Header Type 0普通设备 1桥 2 cardbus

Base Address Register 0~5寄存器

保存设备使用的域地址空间的基地址

桥的配置空间

Subordinate Bus Number当前PCI 子树中,编号最大的PCI 总线号。

Secondary Bus Number 寄存器存放当前PCI 桥使用的总线号

Primary Bus Number 上游总线编号

Bar寄存器

BAR 寄存器保存PCI 设备使用的地址空间的基地址,该基地址保存的是该设备在PCI 总线域中的地址

问题:

bar0空间的其他用途

Bar0不仅仅只用来存储,域的基地址

通过往bar0寄存器全写1来获得该设备的可用空间

图中该设备可认可的空间位2的12次方4K,所以地址必须4K的整数倍

代码中也能看到先读bar0的内容,然后将bar0全写1,在读出的内容就是大小,其bit 31–12

有效,低12bit其他用途,所以地址按4K对齐,不过读大小的时候低12bit读出的值是0.

数据交换

要实现数据交互?

条件?

Who(和谁通信)

如何区分设备(id),如何知道谁是谁

How(怎样通信)

空间转换((ATU)翻译官如何翻译)

格式(TLP包),

PCIe扫描过程

- 软件层面给每个设备一个描述id(BDF)

ID就由Bus+Device+Function组成PCIe协议支持256个Bus,(8bit)

每条Bus最多支持32个Device,(5bit)

每个Device最多支持8个Function(3bit) - Bus:根据DFS(Depth First Search)算法软件分配

Dev:

PCI 设备的IDSEL 信号与PCI 总线的AD[31:0]信号的

连接关系决定了该设备在这条PCI总线的设备号

pcie;硬件决定,桥的口决定dev

Func:硬件决定这个pcie设备有什么功能

ATU

地址转换单元

- 用来实现事务转换和地址转换的功能

- Hisi(ATU)按发送方向和接收方向各提供了8 个地址转换区,每一个区可单独实现某一种事务类型和地址转换功能。其中,

- 发送方向用于将对本地总线地址上的读写操作转换为PCIe 总线地址上的PCIe 事务,

- 接收方向用于将PCIe 总线地址上的PCIe 事务转换为本地总线地址上的读写操作。

hisi寄存器分配

事务

具体是如何操作的

配置事务

存储器事务

配置事务

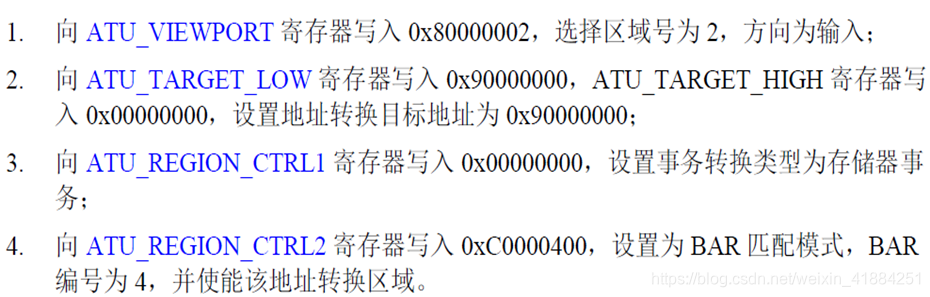

hisi的ATU

存储器事务

##存储器路由

- 这些寄存器都是在PCI域中路由TLP包的时候用的一些窗口寄存器。

- 如果一个TLP mem 读/写 的地址正好落入mem base ~ mem base + mem limit的范围内,则该TLP包从上游总线转到下游 总线上;

- 如果一个TLP包到达桥的下游总线时,其访问的地址不在mem base ~ mem base + mem limit 的范围内时,该TLP包被传送到上游总线。

- 一个访问从CPU域被转换到PCI域,应该使用和具体 实现相关的硬件转换模块,比如ATU。

TLP

PCIe定义了下三层(彩色部分):事务层(Transaction Layer),数据链路层(Data Link Layer)和物理层(Physical Layer)

- 事务层的主要职责是创建(发送)或者解析(接收)TLP (Transaction Layer packet),流量控制,QoS,事务排序等。

- 数据链路层的主要职责是创建(发送)或者解析(接收)DLLP(Data Link Layer packet),Ack/Nak协议(链路层检错和纠错),流控,电源管理等。

- 物理层的主要职责是处理所有的Packet数据物理传输,发送端数据分发到各个Lane传输(stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Scramble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)去扰(De-scramble),以及8/10或者128/130编码解码,等等。

TLP格式

TLP 头由3个或者4个双字(DW)组成。其中第一个双字中保存通用TLP 头,其他字段与通

用TLP 头的Type 字段相关。一个通用TLP 头由Fmt、Type、TC、Length 等字段组成

路由

-

地址路由:

如果一个TLP mem 读/写 的地址正好落入mem base ~ mem base + mem limit的范围内,则该TLP包从上游总线转到下游 总线上;

如果一个TLP包到达桥的下游总线时,其访问的地址不在mem base ~ mem base + mem limit 的范围内时,该TLP包被传送到上游总线。 -

ID路由:

当一个Switch收到一个基于ID寻址的TLP,首先检查TLP中的BDF是否与自己的ID匹配,如匹配,说明该TLP是给自己的,收下;否则,则检查该TLP中的Bus Number是否落在Secondary Bus Number和Subordinate Bus Number之间,如果是,说明该TLP是发给其下游设备的,然后转发到对应的下游端口;如果其他情况,则拒绝这些TLP。