Verilog generate 和for的区别

一直搞不清generate 和for的区别是什么,自己写了个module看看综合后的效果。

generate for

module top_module(

input [7:0] in,

output [7:0] out );//

// assign out[31:24] = ...;

genvar i;

generate

for(i = 0; i < 4; i = i + 1) begin : bit_reverse

assign out = {in,{1'b0}};

end

endgenerate

endmodule

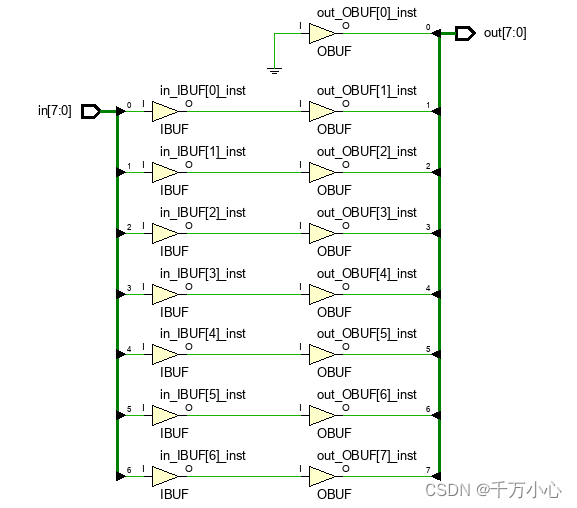

综合后可以看到只有最低1bit为0,其余位向高位移动一位,相当于out = {in,{1’b0}}复制了多份,但是每次效果是一样的

for loop

module top_module(

input [7:0] in,

output [7:0] out );//

// assign out[31:24] = ...;

reg [7:0] in_reg;

always@(*) begin:test

integer i;

in_reg = in;

for(i = 0; i < 4; i = i + 1) begin : bit_reverse

in_reg = {in_reg,{1'b0}};

end

end

assign out = in_reg;

endmodule

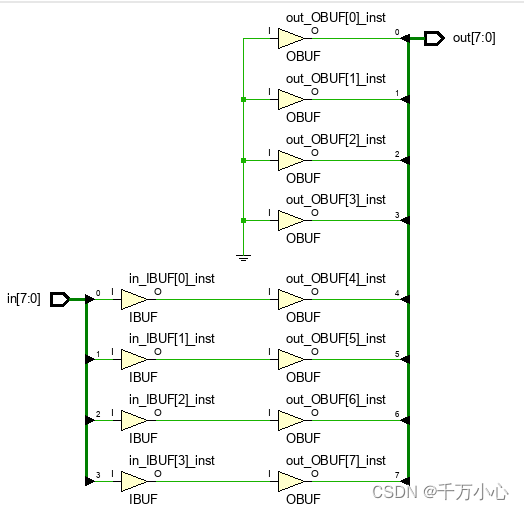

综合后可以看到只有最低4bit变为0,高4bit移动了4次,相当于in_reg = {in_reg,{1’b0}}重复执行了4次。