cdc跨时钟处理

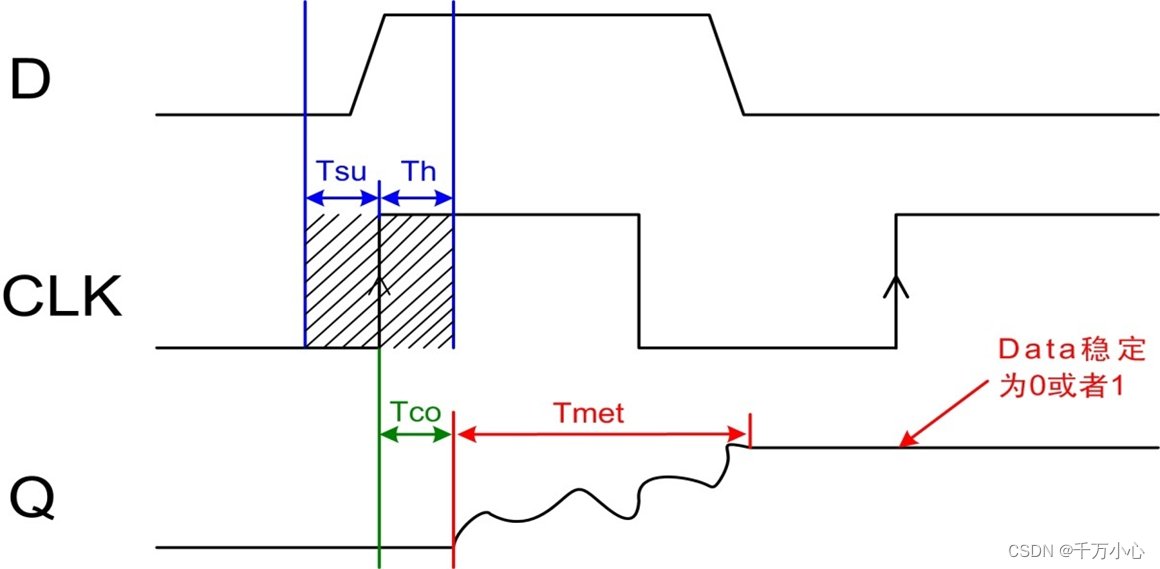

亚稳态 (Metastability):如果数据传输中不满足触发器的建立时间要求和保持时间要求不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值

一旦出现建立时间和保持时间违例,则有可能会导致系统发生亚稳态

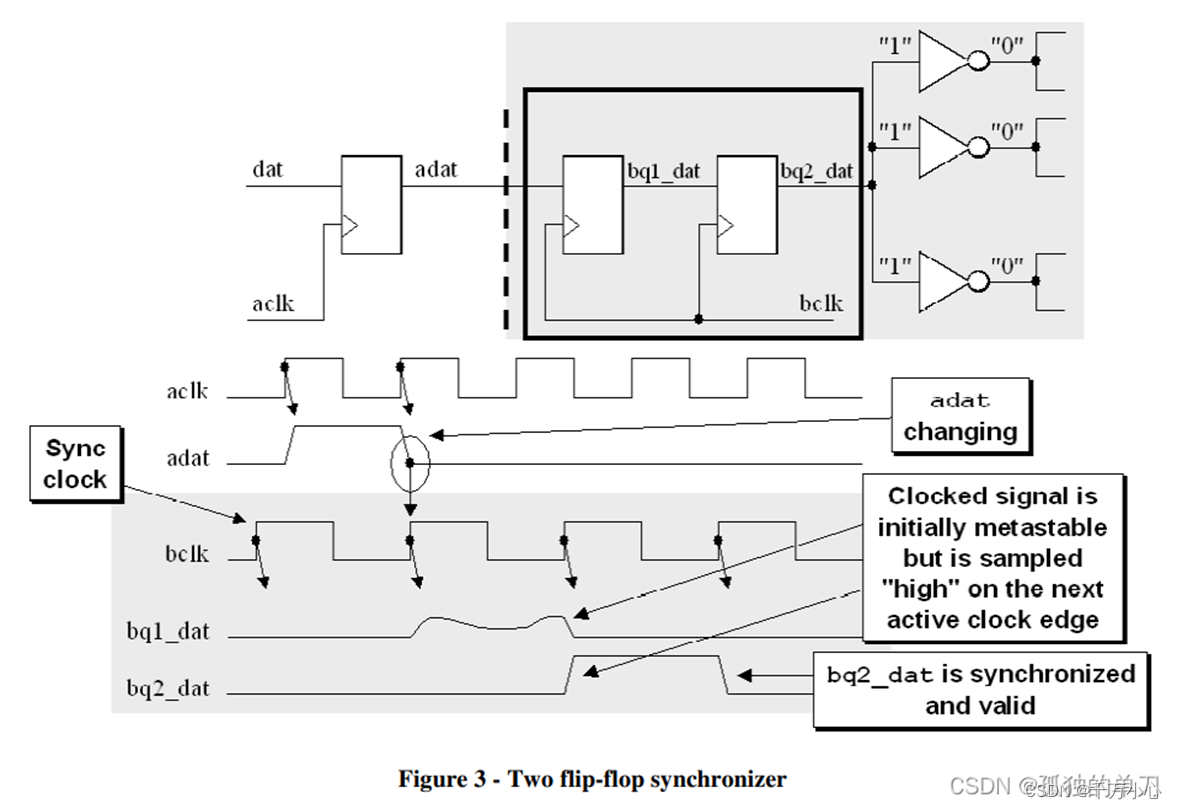

单bit同步处理:两级同步器

1.电平信号:2级或其他级数的同步器

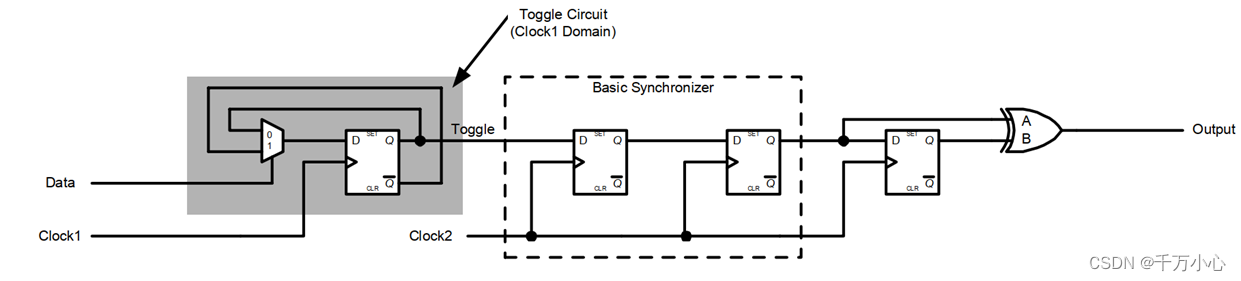

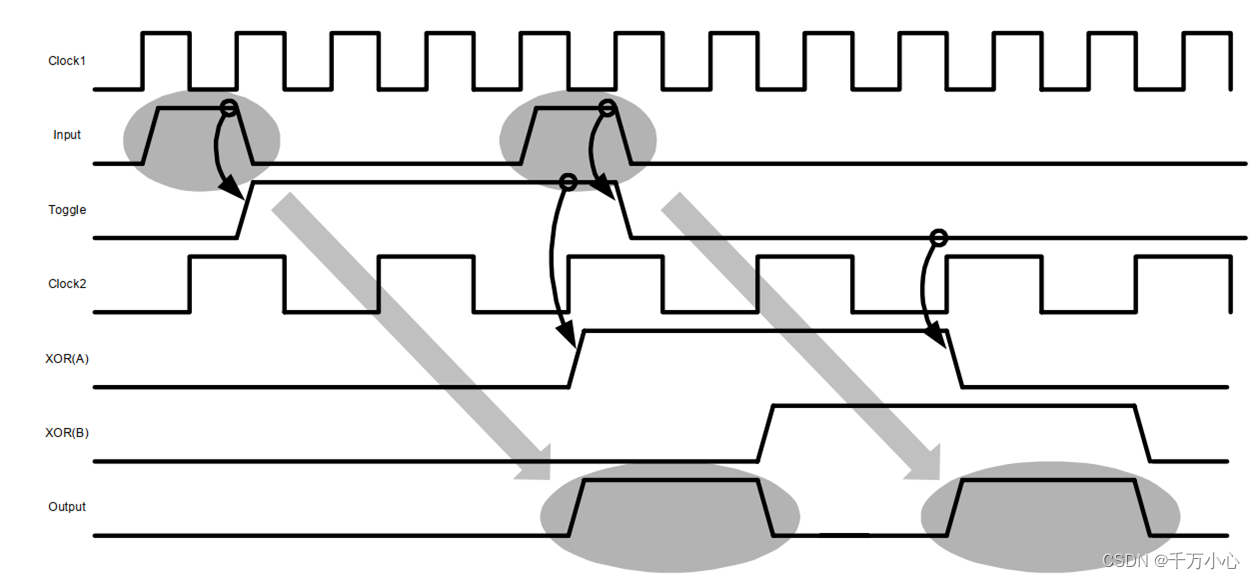

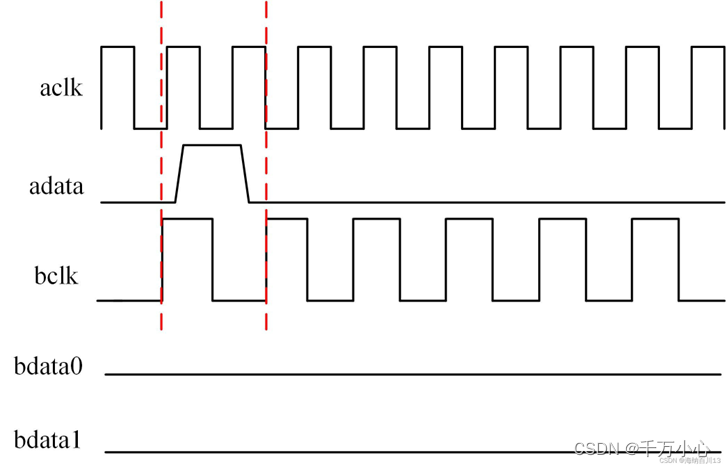

2. 从慢时钟域到快时钟域的脉冲信号(约定快时钟频率应该至少是慢时钟频率的两倍)

3. 从快时钟域到慢时钟域的脉冲信号

处理:信号延展

Data=1时,对输入数据取反

问题:1. 两个脉冲信号距离很近,第二个脉冲信号可能漏采

2. 受限于时钟频率关系

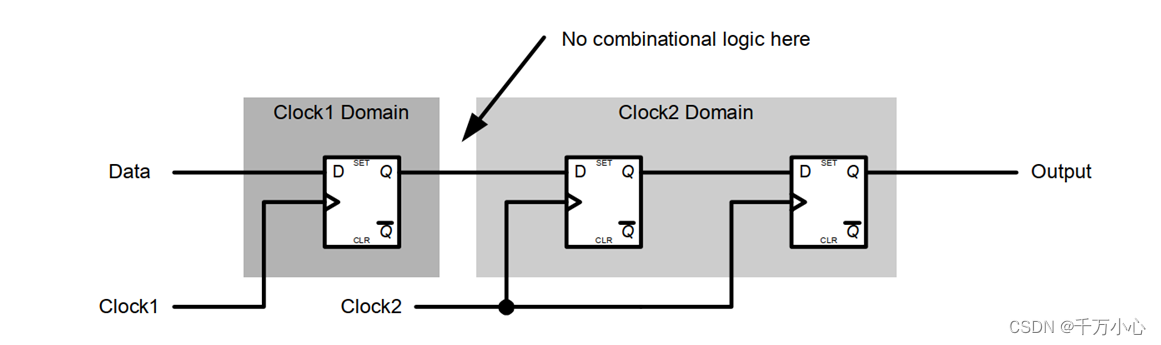

单bit同步器glith

进同步器之前不能有组合逻辑,不然可能产生glitch

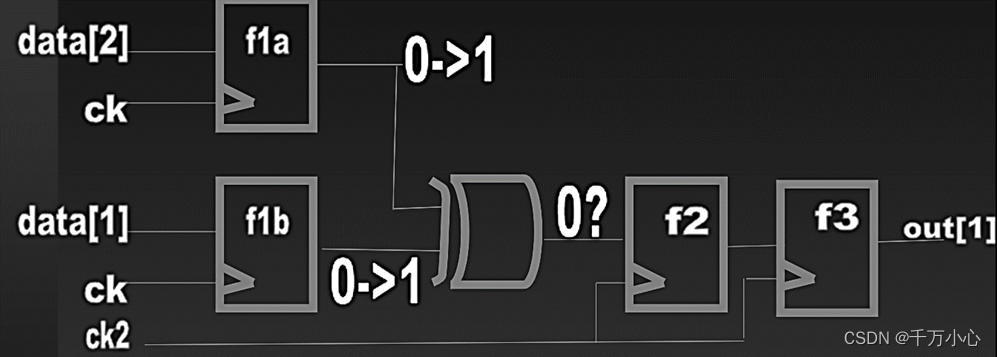

单bit同步器reconvergence(重聚)

在通过不同的同步器后,又进行组合逻辑处理,可能会产生中间态

如:000->111 可能出现 000->001->111

单bit同步处理:握手

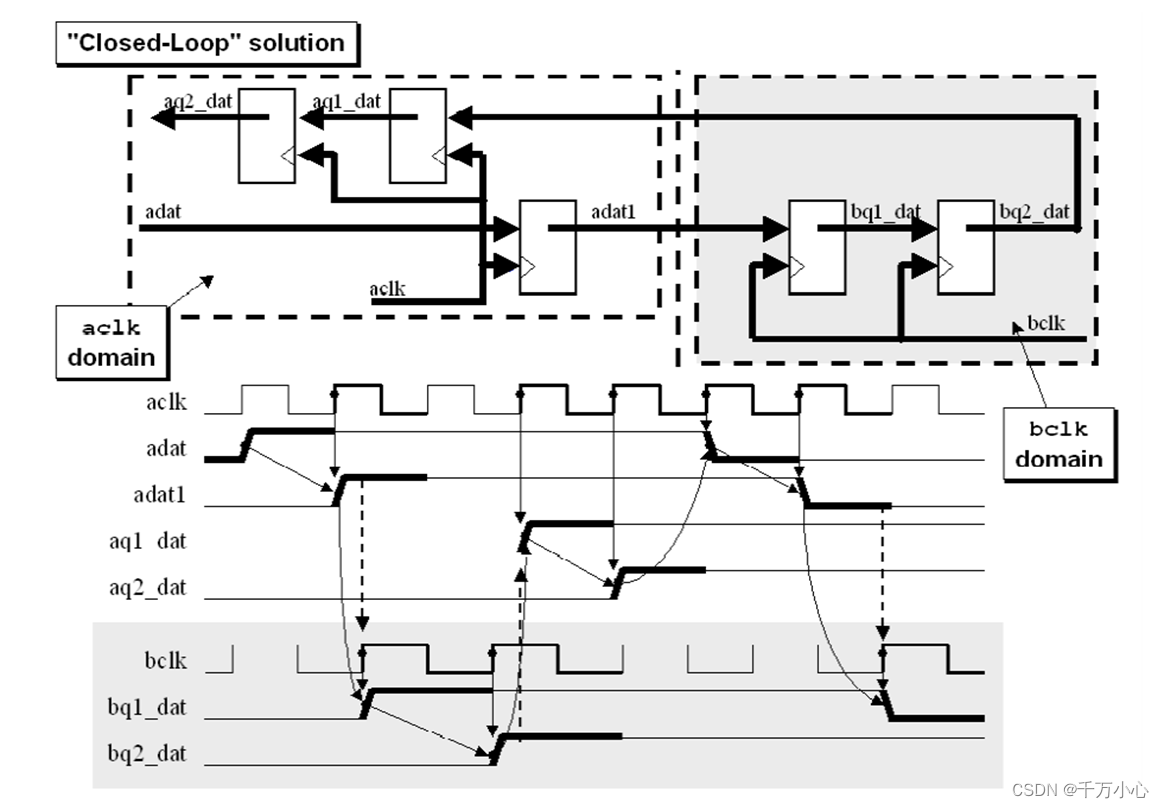

- 源时钟域aclk下的信号adt1信号是要进行CDC的信号;

- adt1先是在源时钟域aclk下被展宽,然后通过两级同步器被同步到目的时钟域bclk下,分别为bq1_dat,bq2_dat;

- bq2_dat作为指示信号(反馈信号,也可以通过bq1_dat和bq2_dat来生成新的指示信号)又被反馈到了目的时钟域aclk下,并进行同步,分别为aq1_dat,aq2_dat;

- aq2_dat的拉高则说明反馈信号的同步完成,此时可以将adt1拉低(结束展宽过程);

- adt1拉低(结束展宽过程)后表示一次CDC操作结束

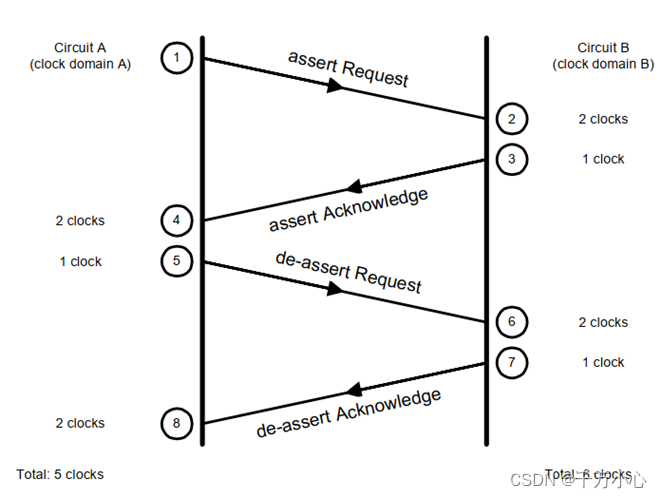

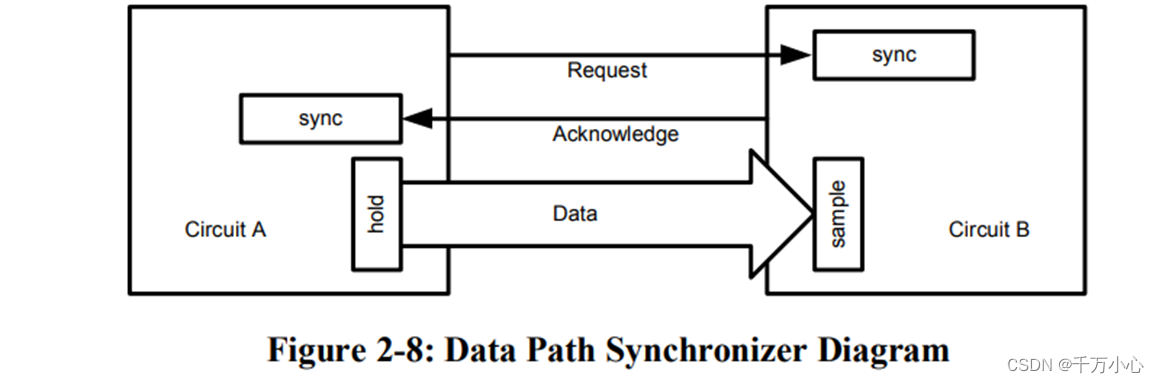

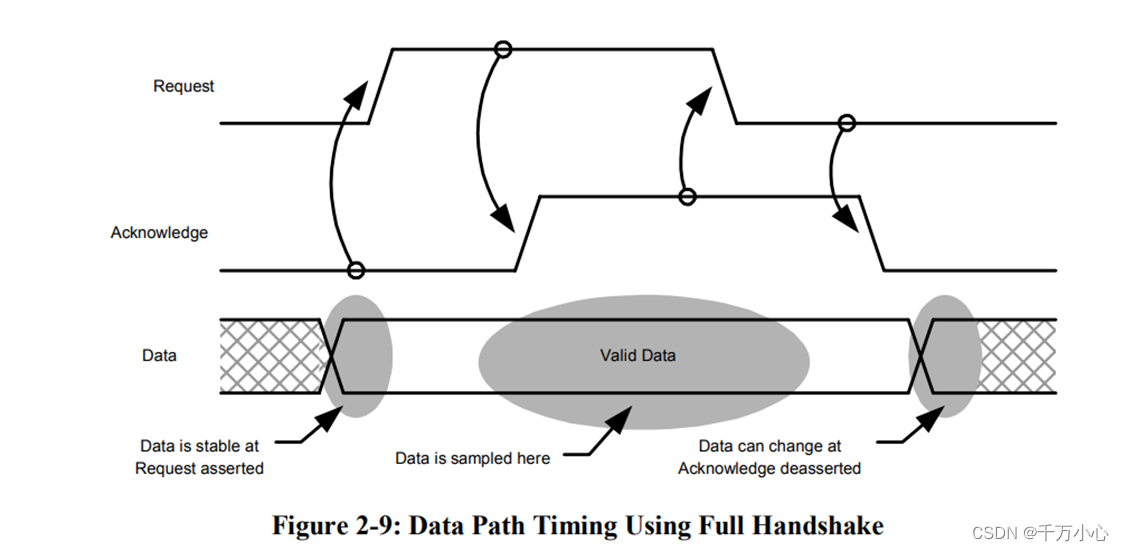

多bit同步处理:握手

- A发起req

- B 检测同步后的req

- B 反馈Ack

- A检测同步后的ack

- A拉低req

- B检测req拉低,随后拉低

7.

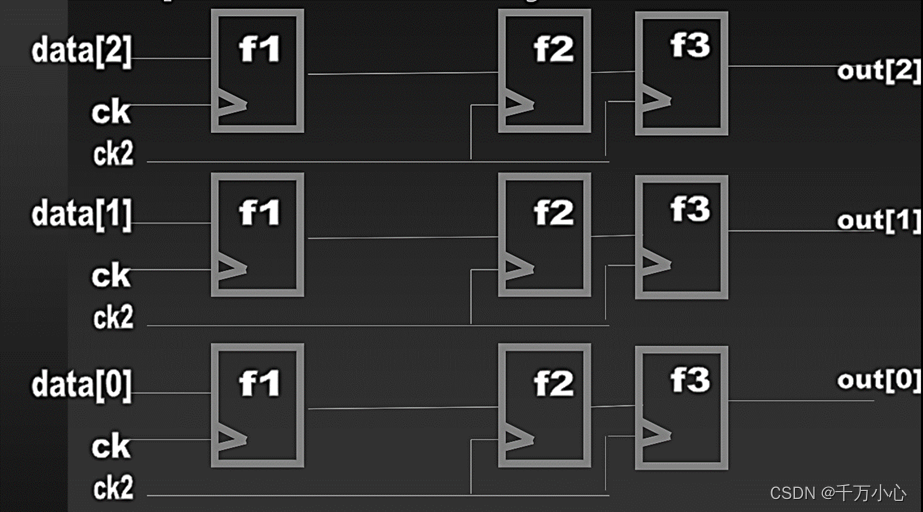

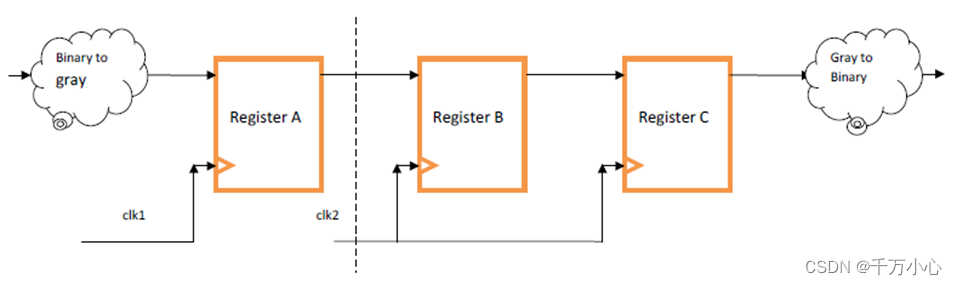

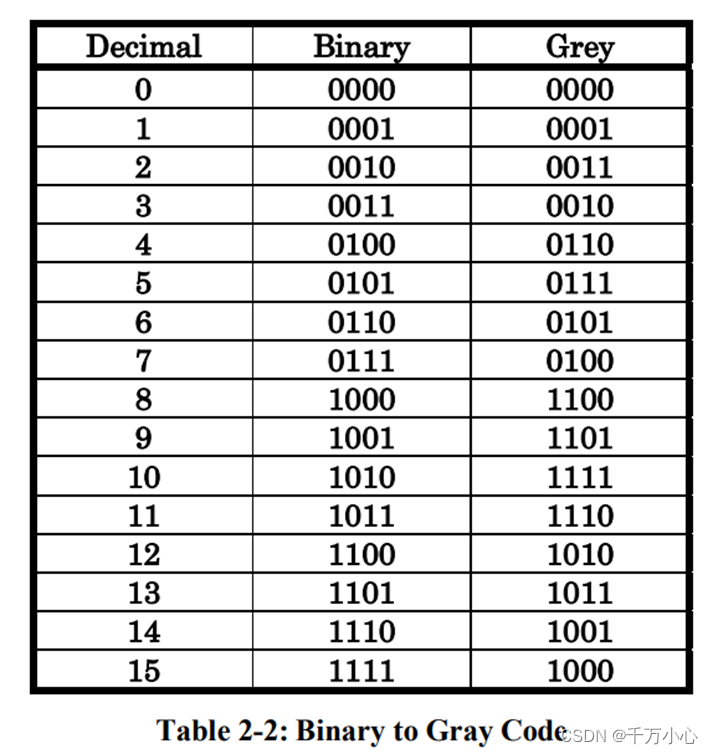

多bit同步处理:格雷码

格雷码每次只有一位发生变化的前提是,数据是递增或递减的,保证异步传输时不会产生额外的中间态

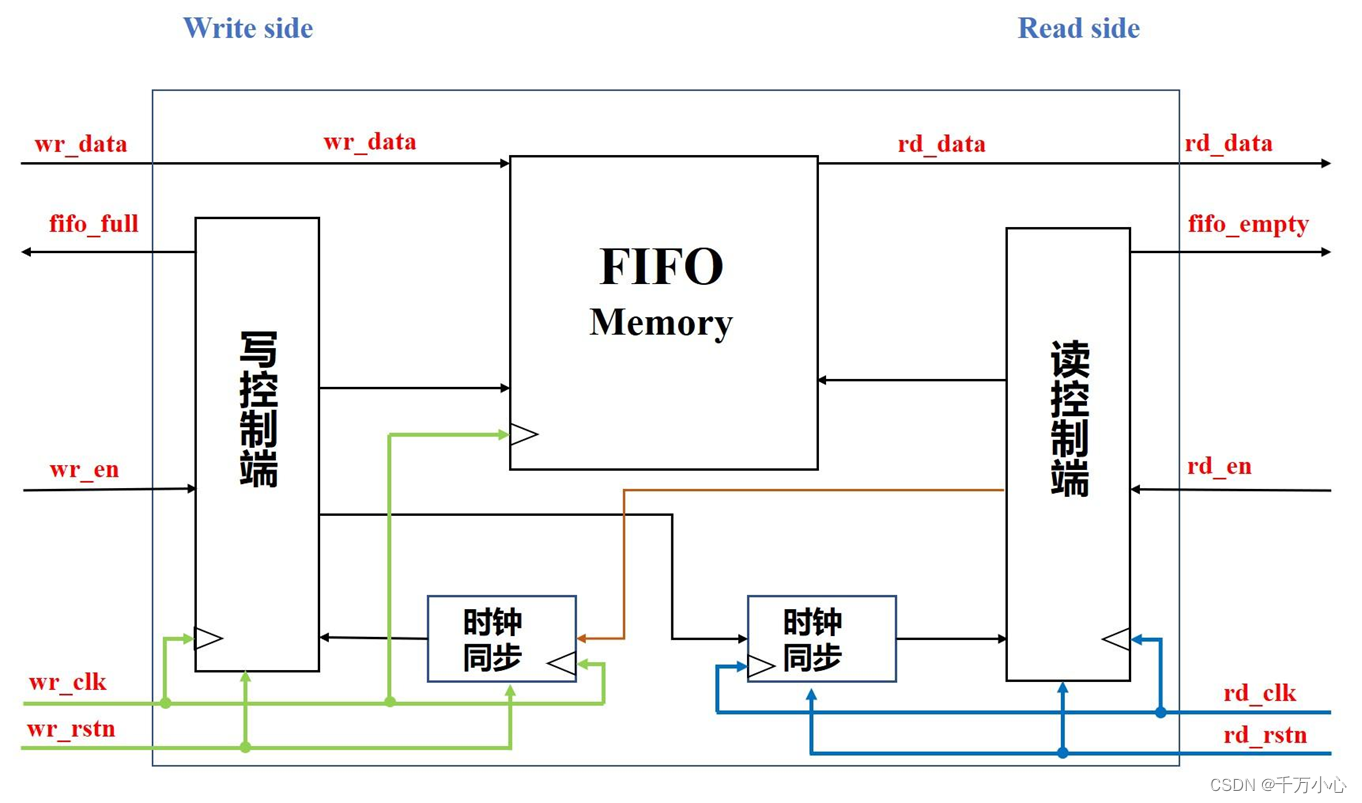

多bit同步处理:异步FIFO

对于不同时钟域的数据传递,则数据可以通过FIFO进行隔离