目录

3.2.5.21 Q8:Design a Mealy FSM(Exams/ece241 2013 q8)

3.2.5.21 Q5a:Serial two's complementer moore FSM(Exams/ece241 2014 q5a)

3.2.5.22 Q5b:Serial two's complementer mealy FSM(Exams/ece241 2014 q5b)

3.2.5.23 Q3a: FSM(Exams/2014 q3fsm)

3.2.5.24 Q3b: FSM(Exams/2014 q3bfsm)

3.2.5.25 Q3c: FSM logic(Exams/2014 q3c)

前言

HDLbits网站如下

Problem sets - HDLBits (01xz.net)

从本期开始我们继续HDLbits第三章Circuits的学习,本期的内容是Finite State Machines有限状态机的第五小节(3.2.5.21-3.2.5.26)

3.2.5.21 Q8:Design a Mealy FSM(Exams/ece241 2013 q8)

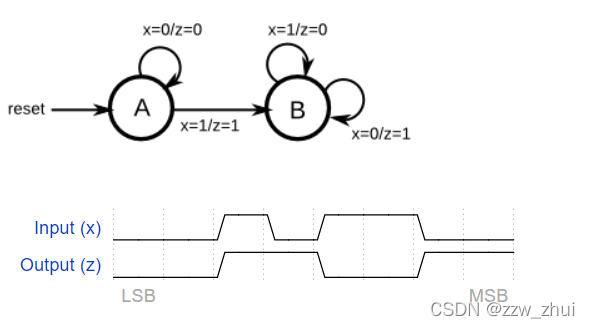

实现一个 Mealy 型有限状态机,该状态机可识别名为 x 的输入信号上的序列"101"。您的 FSM 应具有输出信号 z,当检测到"101"序列时,该信号被判断为逻辑1。FSM 还应具有低电平有效异步复位。状态机中只有 3 个状态。您的 FSM 应识别重叠的序列。

Solution:

module top_module (

input clk,

input aresetn, // Asynchronous active-low reset

input x,

output z );

parameter s0=0,s1=1,s2=2; //s0:0,s1:1--,s2:10--

reg [1:0]state,next;

always@(*) begin

case(state)

s0:next=x?s1:s0;

s1:next=x?s1:s2;

s2:next=x?s1:s0;

endcase

end

always@(posedge clk or negedge aresetn) begin

if(~aresetn)

state<=s0;

else

state<=next;

end

assign z=(state==s2)&x;

endmodule

mealy型状态机,不仅取决于当前状态,还与输入有关,输出信号与输入信号同步,而moore型状态机会慢一拍。

3.2.5.21 Q5a:Serial two's complementer moore FSM(Exams/ece241 2014 q5a)

您将设计一个单输入单输出串行2的补码Moore状态机。输入(X)是一系列位(每个时钟周期一个),从数字的最低有效位开始,输出(Z)是输入的2的补码。机器将接受任意长度的输入数。电路需要异步复位。转换在复位无效时开始,在复位有效时停止。

例如:

Solution:

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A=0,B=1;

reg state,next;

always@(*) begin

case(state)

A:next=x?B:A;

B:next=B;

endcase

end

always@(posedge clk or posedge areset) begin

if(areset)

state<=A;

else

state<=next;

end

always@(posedge clk or posedge areset) begin

if(areset)

z<=0;

else

case(state)

A:z<=x;

B:z<=~x;

endcase

end

endmodule

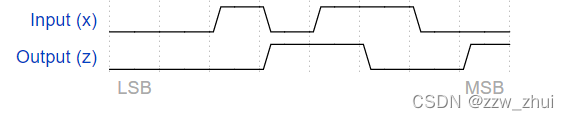

由时序图看出,moore型状态机输出比输入慢了一拍,所以

输入01101000

输出10011000

看出从低位到高位,出现第一个1之前原码与补码相同,出现第一个1之后原码与补码刚好相反。

若输出采用组合always输出,则输出与输入并没有慢一拍

故需要采用时序always输出

3.2.5.22 Q5b:Serial two's complementer mealy FSM(Exams/ece241 2014 q5b)

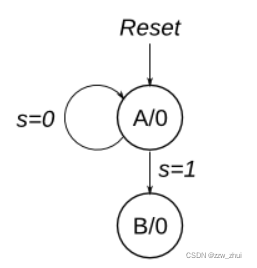

下图是2的补码的Mealy状态机的状态图与时序图。使用独热码实现。

与上一题相反,mealy型状态机输出信号与输入信号同步。

输入:001101000

输出:110011000

Solution:

module top_module (

input clk,

input areset,

input x,

output z

);

parameter A=0,B=1;

reg [1:0]state,next;

always@(*) begin

case(state)

A:next=x?B:A;

B:next=B;

default: next = A;

endcase

end

always@(posedge clk or posedge areset) begin

if(areset)

state<=A;

else

state<=next;

end

assign z=(state==A)?x:~x;

endmodule

3.2.5.23 Q3a: FSM(Exams/2014 q3fsm)

考虑一个具有输入 s 和 w 的有限状态机。假设 FSM 以称为 A 的复位状态开始,如下图所述。只要 s = 0,FSM 就一直保持在状态 A 中,当 s = 1 时,它将移动到状态 B。一旦进入状态 B,FSM 将在接下来的三个时钟周期中检查输入 w 的值。如果 在其中两个时钟周期中w = 1,则 FSM 必须在下一个时钟周期中将输出 z 设置为 1。否则 z 必须为 0。FSM 会继续检查 w 接下来的三个时钟周期,依此类推。下面的时序图说明了不同 w 值所需的 z 值。

使用尽可能少的状态。请注意,s 输入仅在状态 A 中使用,因此只需考虑 w 输入。

Solution:

module top_module (

input clk,

input reset, // Synchronous reset

input s,

input w,

output z

);

parameter A=0,B=1;

reg state,next;

always@(*) begin

case(state)

A:next=s?B:A;

B:next=B;

endcase

end

always@(posedge clk) begin

if(reset)

state<=A;

else

state<=next;

end

reg[1:0]cnt;

reg z1,z2;

always@(posedge clk) begin

if(reset)

cnt<=0;

else if(cnt==2)

cnt<=0;

else if(state==B)

cnt<=cnt+1;

end

always@(posedge clk) begin

if(reset)

begin

z<=0;

z1<=0;

z2<=0;

end

else if(state==B)

begin

if(cnt==0)

begin

z1<=w;

z<=0;

end

else if(cnt==1)

begin

z2<=w;

z<=0;

end

else if(cnt==2)

z<=(z1&z2&~w)|(~z1&z2&w)|(z1&~z2&w);

end

end

endmodule

使用A、B两个状态,使用一个0~2的计数器cnt,cnt=0时寄存器z1存w的值,cnt=1时寄存器z2存w的值,cnt=2时判断z1、z2、w有几个1(有2个1则z为1)

3.2.5.24 Q3b: FSM(Exams/2014 q3bfsm)

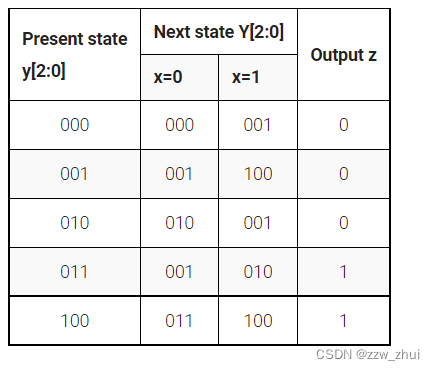

给定如下所示的状态赋值表,实现有限状态机。复位应将 FSM复位为状态 000。

Solution:

module top_module (

input clk,

input reset, // Synchronous reset

input x,

output z

);

parameter s000=0,s001=1,s010=2,s011=3,s100=4;

reg [2:0]state,next;

always@(*) begin

case(state)

s000:next=x?s001:s000;

s001:next=x?s100:s001;

s010:next=x?s001:s010;

s011:next=x?s010:s001;

s100:next=x?s100:s011;

default: next=s000;

endcase

end

always@(posedge clk) begin

if(reset)

state<=s000;

else

state<=next;

end

/*

always@(*) begin

case(state)

s000:z=0;

s001:z=0;

s010:z=0;

s011:z=1;

s100:z=1;

default: z=0;

endcase

end

*/

assign z=(state>=3);

endmodule

输出时巧用状态机,state>=3即为s011、s100

3.2.5.25 Q3c: FSM logic(Exams/2014 q3c)

给定如下所示的状态赋值表,实现逻辑函数Y[0]和z。

Solution:

module top_module (

input clk,

input [2:0] y,

input x,

output Y0,

output z

);

parameter s000=0,s001=1,s010=2,s011=3,s100=4;

reg [2:0]next;

wire [2:0]state;

assign state=y;

always@(*) begin

case(state)

s000:next=x?s001:s000;

s001:next=x?s100:s001;

s010:next=x?s001:s010;

s011:next=x?s010:s001;

s100:next=x?s100:s011;

default: next=s000;

endcase

end

assign Y0=next[0];

assign z=(state>=3);

endmodule

还有两天把FSM搞定