目录

一、实验目的

1. 掌握移位寄存器的工作原理和设计方法。

2. 理解串并数据转换的概念和方法。

二、实验环境

1. 装有ModelSim和VIVADO的计算机。

2. Sword实验系统。

三、实验任务

1. 用VerilogHDL语言设计实现8位带并行输入的右移移位寄存器,在ModelSim上实现功能仿真。

2. 生成FPGA设计文件,下载到Sword实验系统上验证电路功能。

四、实验原理与实验步骤

1. 实验原理

在移位寄存器中,要求每来一个时钟脉冲,寄存器中的数据就会按顺序向左或者向右移动一位。因此,在构成移位寄存器时,必须采用主-从触发器或者边沿触发器,而不能采用电平触发器。

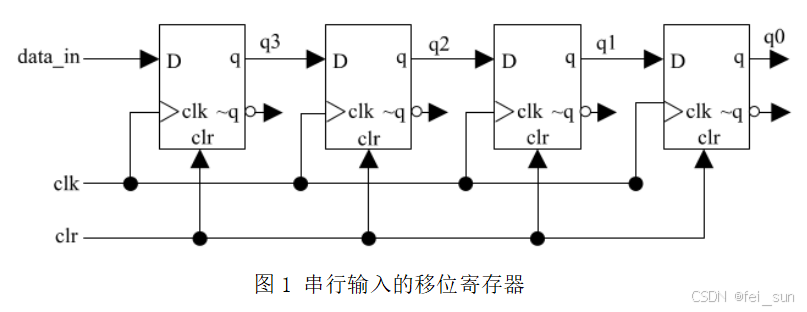

数据输入移位寄存器的方式有串行输入和并行输入两种。下图是串行输入移位寄存器。在时钟的作用下,输入数据进入移位寄存器最左位,同时,将已存入寄存器的数据右移一位。并行输入方式是把全部输入数据同时存入寄存器。

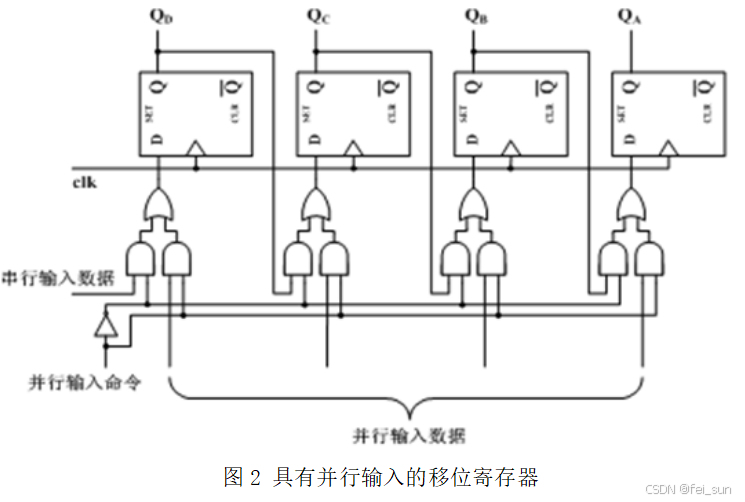

下图是具有串行和并行输入的8位右移移位寄存器模块。

通过并行输入命令选择是串行输入还是并行输入。

2. 实验步骤

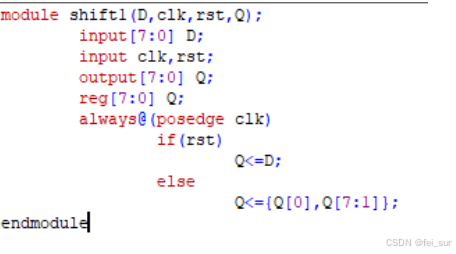

(1)用Verilog语言采用结构描述或者行为描述方法设计一个仅带有8bit并行输入的右移移位寄存器。

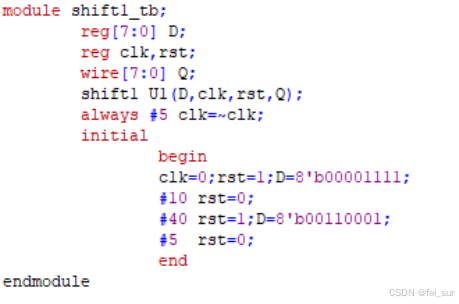

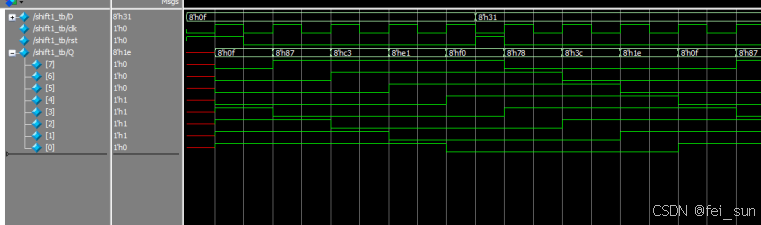

(2)编写测试模块,完成modelsim下电路的功能仿真,验证电路功能。

(3)建立完成I/O引脚分配。

系统时钟为100MHz,从提供的clkdiv引出clkdiv[24]作为移位控制时钟。

测试移位寄存器时采用开关SW[0]~ SW[7]作为移位寄存器的并行输入,SW[15]作为clr信号,将输出显示在led[0]~led[7]上(或同时显示到led和数码管上)。设置相应的约束文件。

设计实现实验原理中图2“带有并行输入的移位寄存器”电路模块,并在modelsim下完成电路仿真。

SW[9]作为选择串行还是并行,SW[8]作为串行输入

top.v

module TOP(input wire clk_100mhz,

// I/O:

input wire[15:0]SW,

output wire led_clk,

output wire led_clrn,

output wire led_sout,

output wire LED_PEN,

output wire seg_clk,

output wire seg_clrn,

output wire seg_sout,

output wire SEG_PEN

);

wire[31:0]Div;

wire[15:0]LED_DATA;

wire CK;

wire[63:0] disp_data;

wire[7:0] out;

shift2 U1(SW[7:0],Div[24],SW[15],out,SW[8],SW[9]);

shumaguan U3(disp_data[63:56],out[3:0]);

shumaguan U4(disp_data[55:48],out[7:4]);

clk_div U8(clk_100mhz,1'b0,SW[2],Div,CK);

assign disp_data[47:0]=48'hffffffffffff;

P2S #(.DATA_BITS(64),.DATA_COUNT_BITS(6))

P7SEG (clk_100mhz,

1'b0,

Div[20],

disp_data,

seg_clk,

seg_clrn,

seg_sout,

SEG_PEN

);

LED_P2S #(.DATA_BITS(16),.DATA_COUNT_BITS(4))

PLED (clk_100mhz,

1'b0,

Div[20],

LED_DATA,

led_clk,

led_clrn,

led_sout,

LED_PEN

);

assign LED_DATA = ~{out[0],out[1],out[2],out[3],out[4],out[5],out[6],out[7],1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0,1'b0};

endmodule

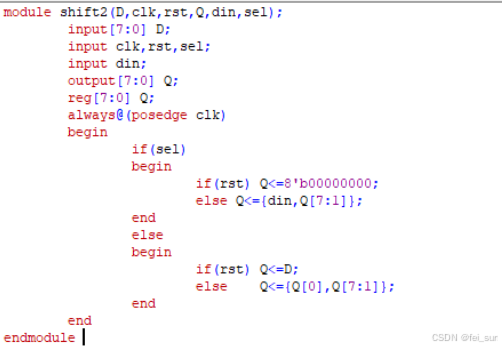

shift2.v

module shift2(D,clk,rst,Q,din,sel);

input[7:0] D;

input clk,rst,sel;

input din;

output[7:0] Q;

reg[7:0] Q;

always@(posedge clk)

begin

if(sel)

begin

if(rst) Q<=8'b00000000;

else Q<={din,Q[7:1]};

end

else

begin

if(rst) Q<=D;

else Q<={Q[0],Q[7:1]};

end

end

endmodule shumaguan.v