为高频交易(High Frequency Trading,HFT)公司开发硬件一直是 FPGA 工程师最热门的职位之一。由于该行业提供的高薪,甚至可以被称为该领域许多人的“梦想职业”。本文根据自己和其他人的亲身经历,写了一篇关于测试职位是什么样子以及如何准备面试的文章。

HFT 世界是什么样的

为了理解这些术语并以更合适的方式做好准备,我们首先来谈谈 HFT 是什么,以及为什么 FPGA 在交易行业中占有一席之地。

高频交易是算法交易(https://www.investopedia.com/articles/active-trading/101014/basics-algorithmic-trading-concepts-and-examples.asp)的一种变体,算法交易本身是自动日间交易的一种变体,从根本上讲,是由算法而不是人来下订单。人编写和监控算法,但不手动下交易。在 HFT 中,所有这些都被推向极致,利用可能只持续几毫秒的机会,通常是套利机会。为了有效地利用这样的机会并赚钱,人们需要在极短的时间内消化市场数据、做出决策并下大量订单。这就是比赛的开始。

在那本令人惊叹的书《Trading at the speed of Light,光速交易》中,唐纳德·麦肯齐解释了即使在芝加哥场内交易的日子里,人们也通过创建系统来适应环境,使某些人的交易速度比其他人快得多。本质上,设计交易是一个可以利用信息不对称的游戏,如果此时你有一些信息尚未传达给其他人,那么就存在一种不对称,你可以预测其他人在获得这些信息后会做什么,并据此做出决定。这种不对称是套利机会和许多其他可以赚钱的复杂场景的基础。由于交易所本身所使用的技术的重大进步,这些不对称的机会已经变得极为罕见且短暂。

然而,事实是,仅仅因为离交易所较近的人比离交易所较远的人获取数据的速度更快,也就无法消除这种不对称现象。那些能够更快传输数据的人也是如此(微波塔、租用光纤线路)。同样,那些能够在收到数据后做出更快决策的人也可以在这场竞争中领先。这正是 HFT 公司聘请 FPGA 工程师来帮助解决的问题。

交易所允许公司在附近的特定建筑物中设置计算机。无论与哪个股票经纪人交易,那里可能都有一台机器。这称为主机托管。交易所确保从这些机器到交易所计算机的光纤长度对于主机托管中的每个参与者来说都是完全相同的。

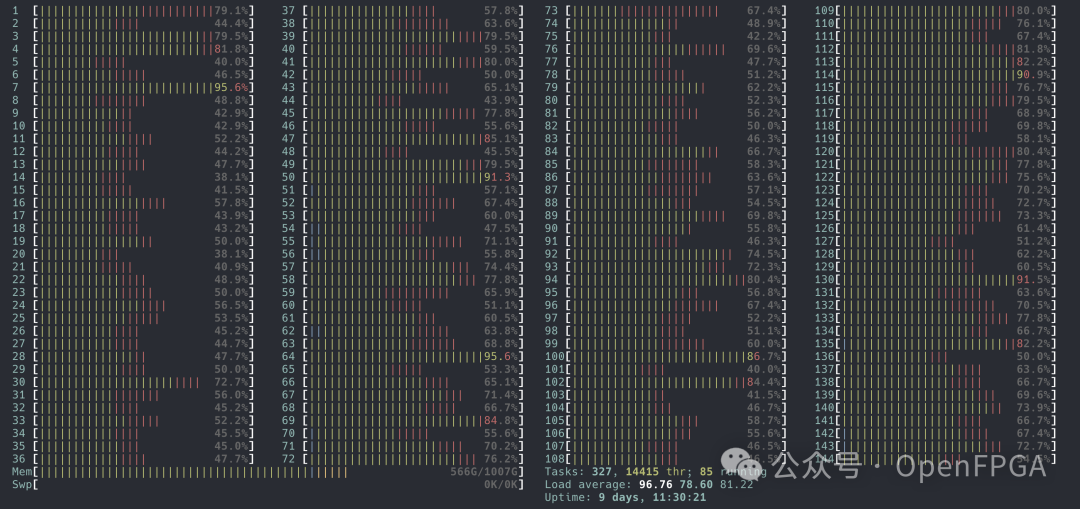

在这种情况下,再靠近交易所的空间已经不大了。不过,我们可以做的是尽量减少消化数据和发出订单所需的时间。为了实现这一点,这些服务器在处理速度、内存速度和延迟方面都拥有极高的规格。它们被超频并优化到了它们所能提供的极限。

尽管进行了这些优化,但 CPU 从根本上来说仍存在两个对 HFT 不太友好的”怪癖“。

更高的执行延迟

CPU 需要将算法分解为 ISA 并按顺序执行,尽管速度可能很快,由于关键路径中有几个交互元素,在处理交互元素的过程会产生很大的开销。

不确定的执行延迟

交易算法并不是 CPU 上运行的唯一程序。操作系统同时管理着许多进程和线程。这可能导致同一程序在不同执行中花费的时间不同。对于那些押注大量资金并保证该过程将花费一定时间的人来说,这可能是一个巨大的问题。如果只是这一次花费的时间长,就可能意味着巨额损失。

FPGA 如何提供帮助

FPGA 可帮助解决上述两个主要问题。它们能解决不确定性问题。可以预先知道某种操作在 FPGA 中需要多少个时钟周期,并确保在整个操作过程中它不会发生变化。

FPGA 还经常(并非总是)帮助解决高处理延迟的问题。在解码市场数据 -> 做出决策 -> 发送订单的整个流程中,多个子功能可以使用基于 FPGA 的加速。

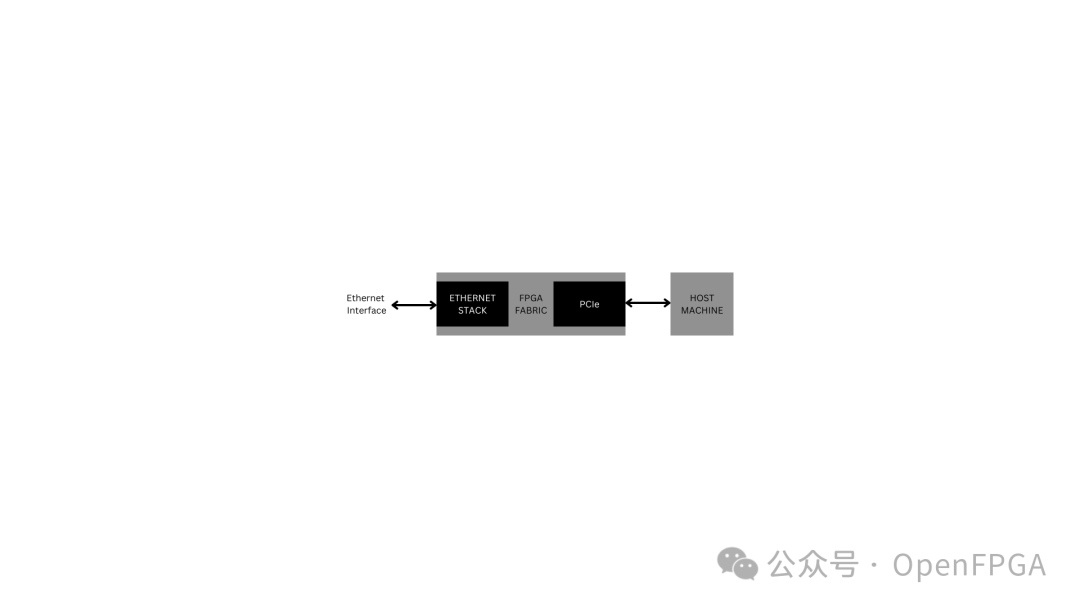

FPGA 不能很好地处理复杂的数学运算,因此工程师们仔细分析了它们的处理管道,并找出了实现选择性过程大幅加速的方法。以下是与 FPGA 连接的交易机的处理流程:

截至今天,市场上有许多流行的开发板,通过处理诸如以太网和 PCIe 之类的一些棘手的模块,为 HFT 相关的 FPGA 开发提供工作台。

面试准备

现在,对HFT世界有了一个很好的印象,我希望对使用这些尖端工具的兴趣会越来越浓厚。让我们来谈谈作为 HFT FPGA 工程师在日常工作中需要具备的技能。

数字电路和 RTL 设计

精通数字逻辑、Verilog 和微架构开发。

这些是基础。应聘者需要具备编写 RTL、调试和在板上部署 RTL 的经验。面试通常要求应聘者当场编写 RTL。

问题陈述也可能相当复杂和令人费解,与传统的 FPGA 工作(例如网络或国防工业)不同。这既考验应聘者的智商,也考验应聘者的 RTL 技能。

公司非常重视编写花费更少时间来完成某项任务的代码,这通常需要集思广益,想出完成同一件事的不同方法,并提出一种低延迟的替代方案,同时保持足够合理以便在限制时间内实现。

状态机编码:状态机是FPGA中另一个非常常见的模块。

先进先出(FIFO):FIFO 无处不在,同步、异步等各种类型。

验证基础知识:

如前所述,FPGA 团队在 HFT 中规模很小,因此单个开发人员必须身兼数职才能完成一个项目。此外,由于交易规模巨大(一次数百万美元),设计中的一个错误就可能导致损失大量资金,损失金额可能相当于几年的年薪。

因此验证成为一项非常重要的任务。尽管 FPGA 可以多次重新编程,但风险很高,必须小心谨慎,确保不会出现任何错误。

为代码编写高效的测试台和测试用例是一项宝贵的技能。对于经验更丰富的人,了解 System Verilog 和 UVM 可能是一个加分点。

网络基础知识:

工作中实际实施的项目通常围绕网络展开。

传入的市场数据通过 TCP 通道传输,交易机器需要维护 TCP 连接,这可能是另一个潜在加速的领域。

类似地,可能需要过滤一些数据,并将其打包成数据包发送到不同的地方(通常是另一个交换机)。TCP 或 UDP 可用于通信的这一部分,这也是一种很好的加速方式。

掌握以太网协议及其细节的基本知识在竞争中保持领先大有帮助。

以太网、PCIe 和网络架构(可选、高级):

许多资金雄厚的大公司自己实现相关的协议栈。但大多数其他公司直接使用经过验证的 IP。只有少数大公司才需要以下技能。

对于以太网,需要掌握的知识非常丰富,包括对 SERDES、PHY 与 PCS 层功能、MAC 层功能以及针对特定目的的潜在优化的理解。如果没有在行业环境中进行过相关实践,很难获得这些知识和经验。

推荐下面的文章:

https://support.ixiacom.com/sites/default/files/resources/whitepaper/PCS_white_paper.pdf

PCIe 属于同一类别。它是另一种广泛的协议,包含大量细节和文档。除非初学者使用过它,否则几乎不可能知道这些。但是,有一些宏观概念总是好的。

同样,FPGA 并不是网络上唯一的机器,还有许多其他东西,如交换机、NIC、其他交易机器等,它们可以在做出决策时进行交互操作。对网络架构有充分的了解,并且知道可以调整哪些方面以获得那一点点延迟优势,这可能是一个很大的优势。

实用技巧:

静态时序分析(STA)

对于初学者来说,静态时序分析是一种测试逻辑是否满足 FPGA 时序约束和可靠功能的方法。如上所述,推荐下面的文章

https://thedatabus.io/interview_list

这一点非常重要。通常,由于对延迟极其敏感,HFT 应用的 RTL 是用非常低的流水线编写的,可以在更少的时钟内完成大量工作。这显然会导致综合、布局布线工具将 LUT 放置得非常近,以改善延迟。

一旦完成并验证了 RTL 编码,由于这种拥塞,工具可能无法满足设计的 FPGA 的时序,这种情况很常见。这就需要对 STA 有很深的了解,才能处理逻辑并重新构建它以尝试满足时序。

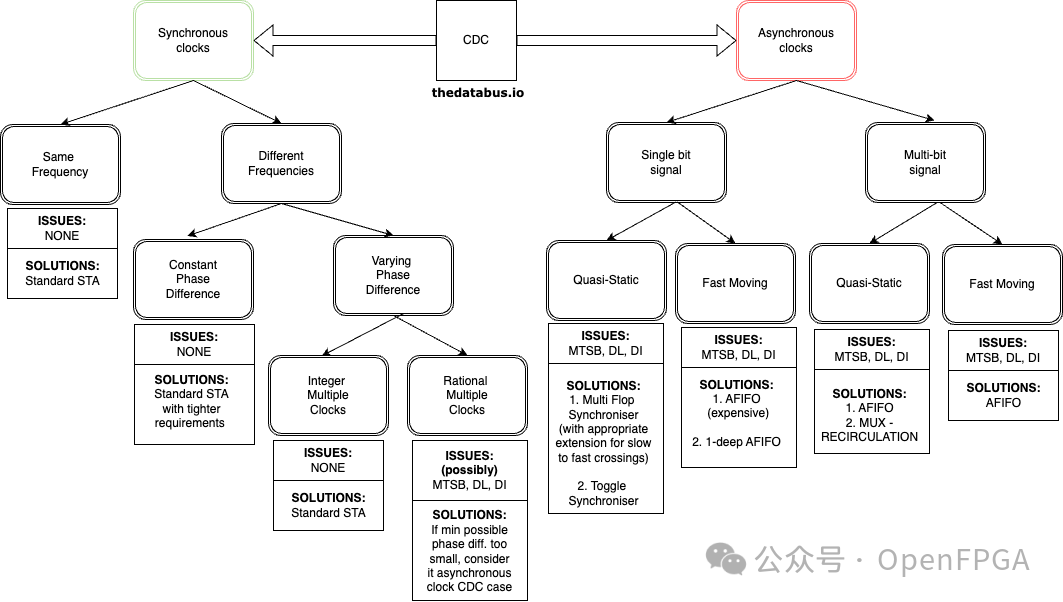

跨时钟域 (CDC)

这是任何 RTL 设计师都需要的一项基本技能,无论是否需要 HFT。几乎每个面试官在完成 STA 后都会询问你所了解的不同 CDC 技术。他们甚至可能会问你为什么一种方法比另一种更好,甚至可能让你编写一些代码。

去读一下关于 CDC 的这篇文章,或许对你有所帮助

https://thedatabus.in/cdc_complete_guide

假设使用双触发同步器执行 CDC,你会为该元素向 .xdc 文件(约束文件)添加哪些约束?ASFIFO 呢?

区域优化

这与前面提到的时序优化密切相关。

HFT 应用的设计通常不是很大,它们不会占据 FPGA 的大部分空间,但逻辑元件彼此之间距离太近,导致拥塞引发各种问题。解决此问题的唯一方法是准确了解 RTL 推断的内容,以及如何对其进行修改以减少拥塞。

通常,对 FPGA 架构及其基本元素(LUT、BRAM、DSP 等)的良好了解可以很好的做出决策。

此外,与其只是编写 RTL 并对其进行仿真,不如将其贯穿整个实施流程(综合、布局和布线等),这样可以更深入地了解 RTL 在到达硅片时最终会发生什么。下一步是尝试以一种能够减少资源利用率和设备区域拥塞的方式控制这种“推断”。

硬件测试

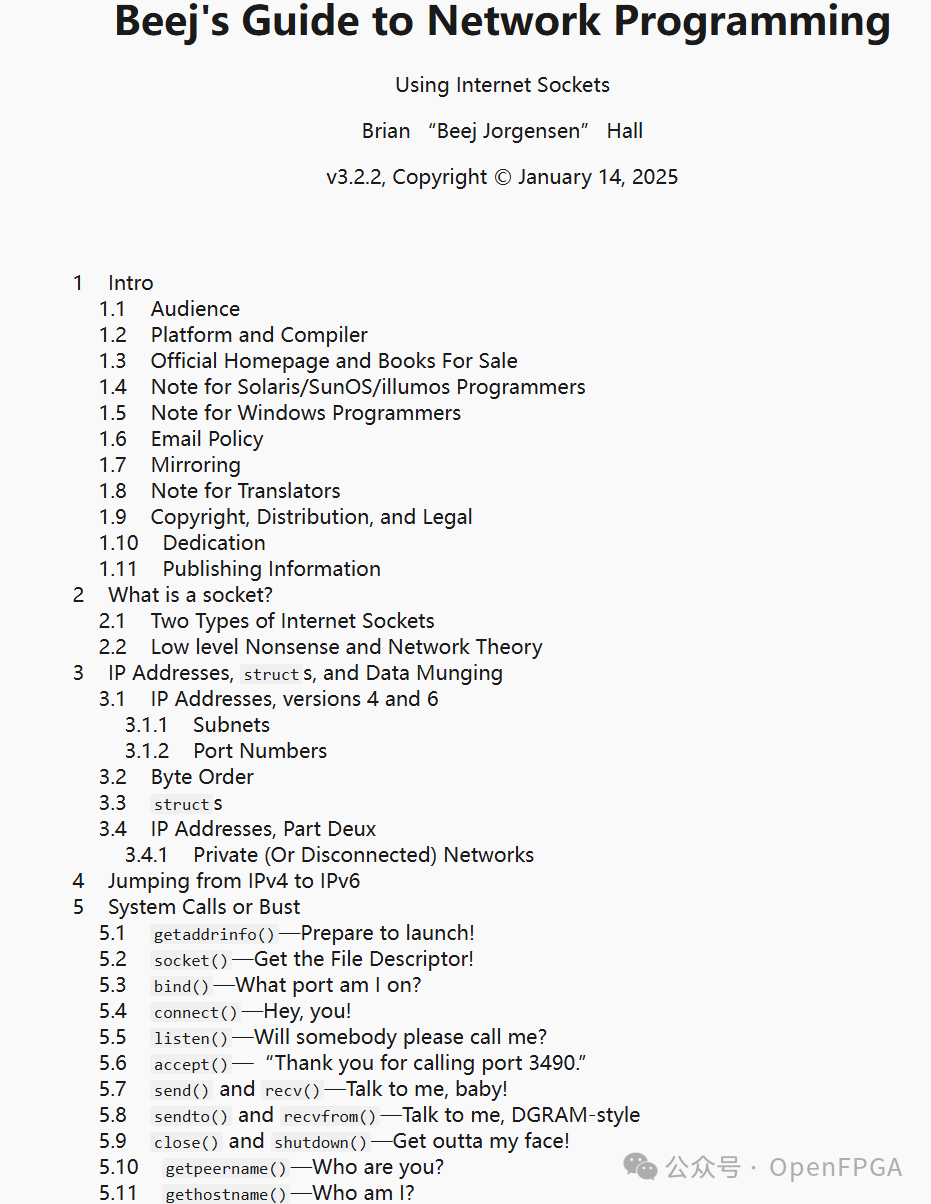

网络知识

https://beej.us/guide/bgnet/html/#intro

把这本书从头到尾读一遍,然后尝试在基于 Linux 的计算机上练习所有内容。

以太网实践知识

以太网知识是HFT工作的必需品。学会一些调试工具(如wireshark等工具)的使用。

在此过程中,还将使用许多 Linux 命令。

C++ 和驱动程序

在任何类型的嵌入式系统中,例如带有 FPGA 的交易机,都需要编写与硬件对话的驱动程序。作为 FPGA 开发人员,需要至少在一定程度上完成这项工作,这足以在真实硬件上测试设计,并为实际软件人员提供概念验证。

金融和交易知识

这不是必需的,也不会要求了解或学习这一点。

DSA/计算机科学技能

通常在编写任何代码时,为了处理数据或测试硬件,将编写大量软件。编写良好的代码可以大大减少使其运行并完成手头任务所需的时间。本着这种精神,如果面试官问你几个与数据结构和算法相关的问题,也不要感到惊讶。

总结

本文是国外的一个朋友在准备相关行业面试的时候总结的一篇文章,和国内可能会有所差异,但是可以作为参考,有从事相关行业的大佬可以在评论区聊聊从事该行业的注意点~

PS:前面提到的《光速交易》这本书非常有趣,即使没有在相关行业工作,它也能让你对这个世界有很深的了解。