1.安装quartus

2.更新usb blaster驱动

3.新建工程

1.随便找一个文件夹,里面新建demo文件夹,表示一个个工程

在demo文件夹里面,新建src(源码),prj(项目),doc(文档)

2.进去quartus里面,点击new project

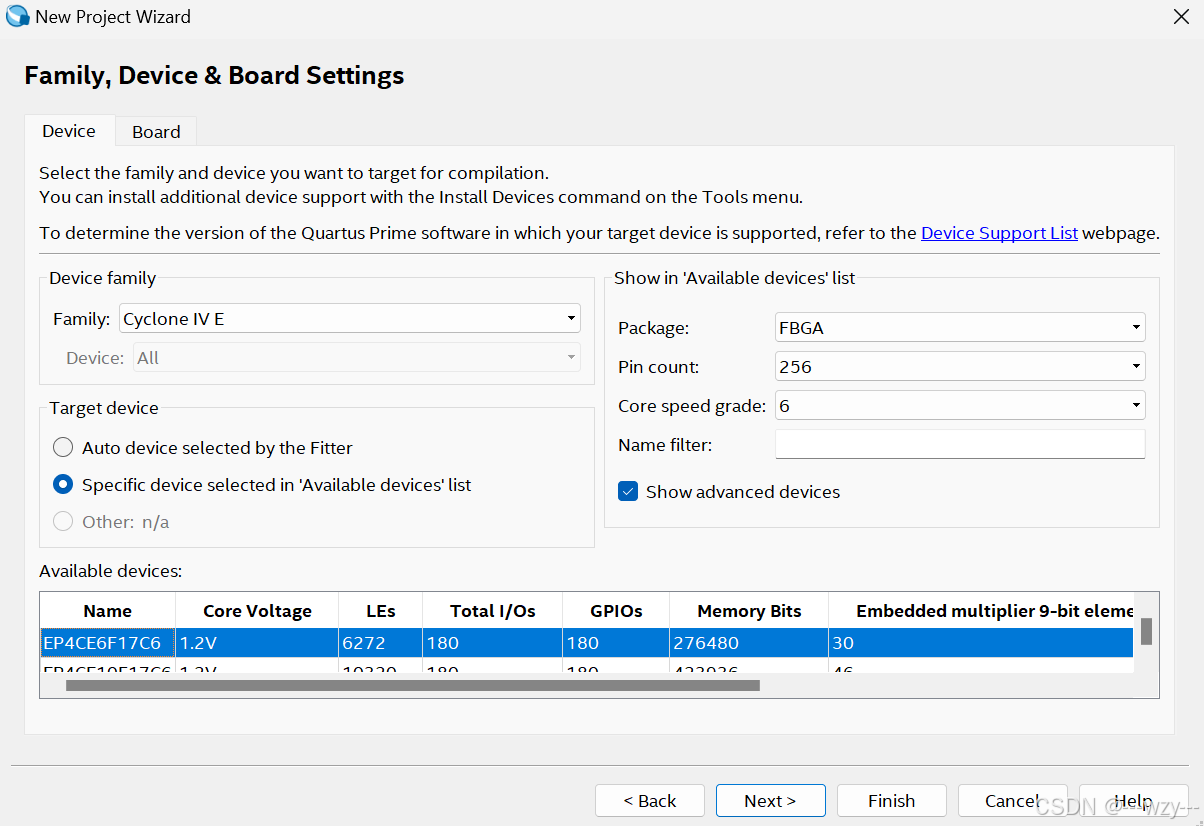

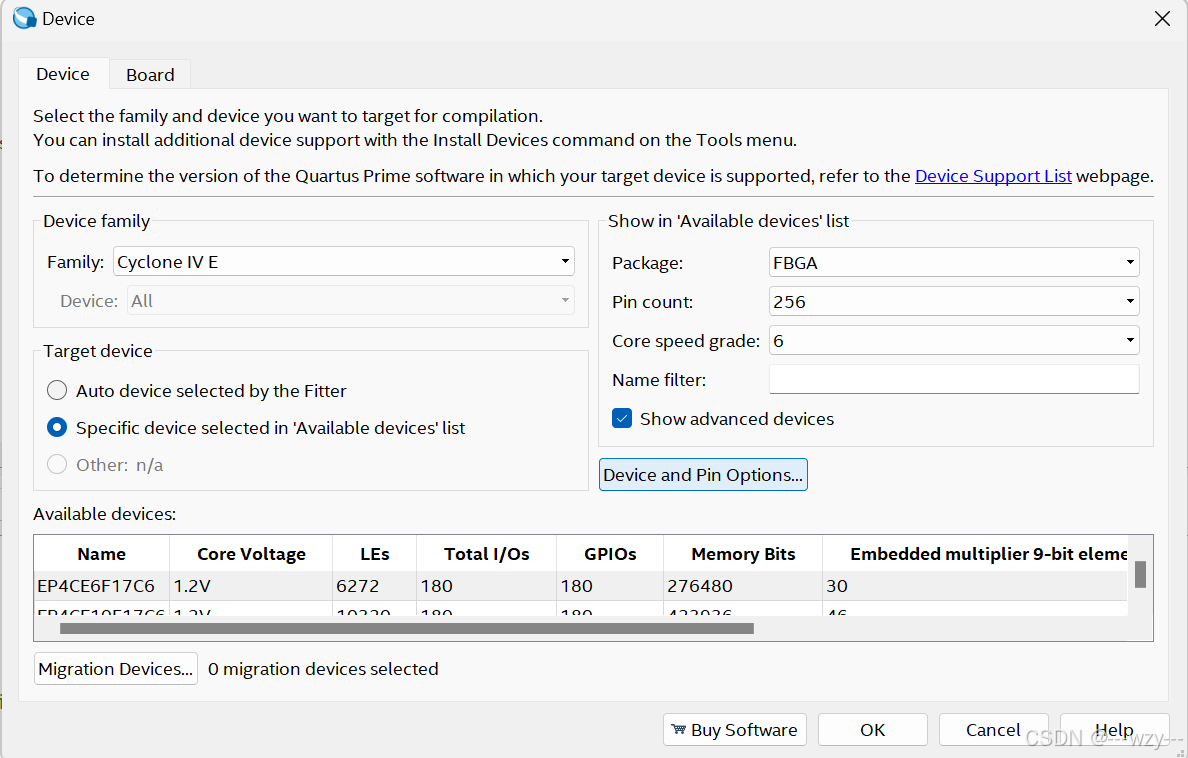

下面是你的fpga开发板的配置,包括Pin count,Core speed grade

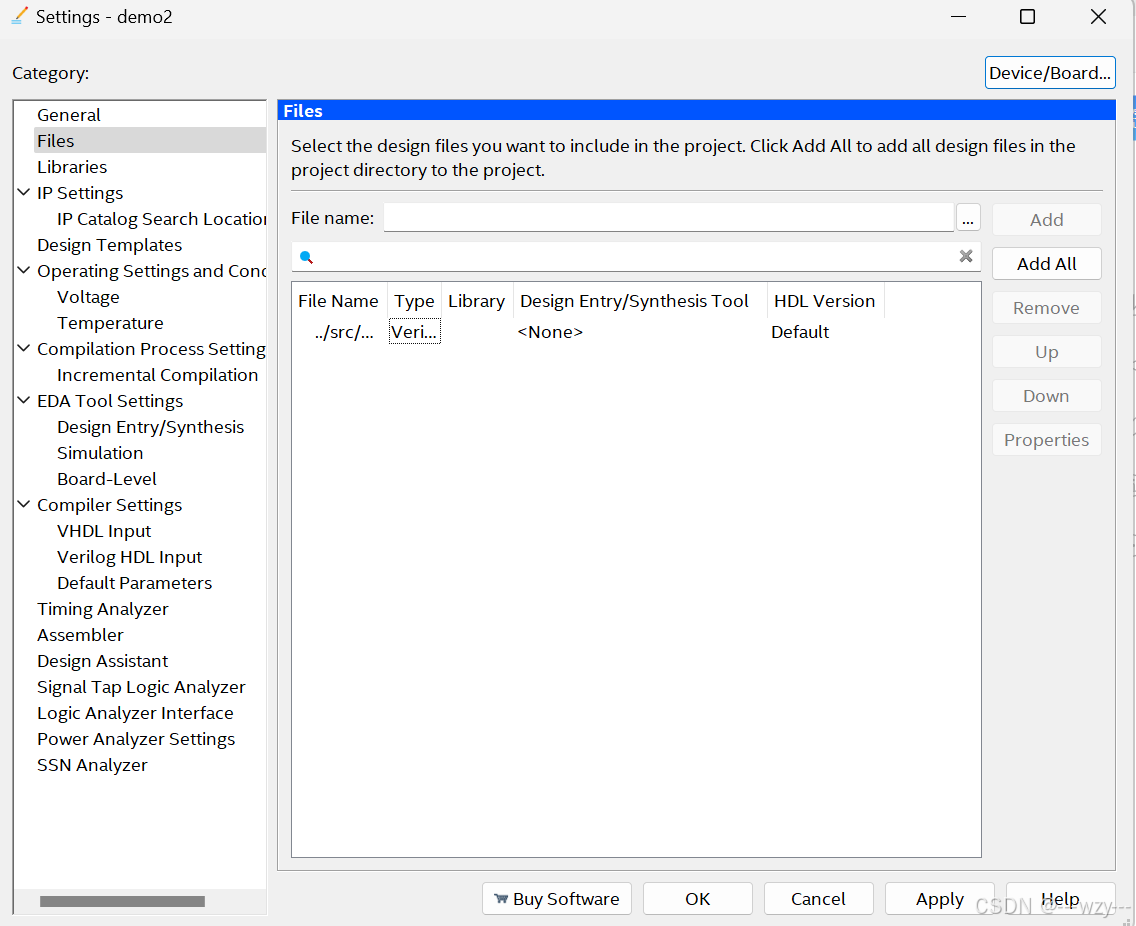

打开工程

"D:\Desktop\fpga\demo2\prj\demo2.qsf"

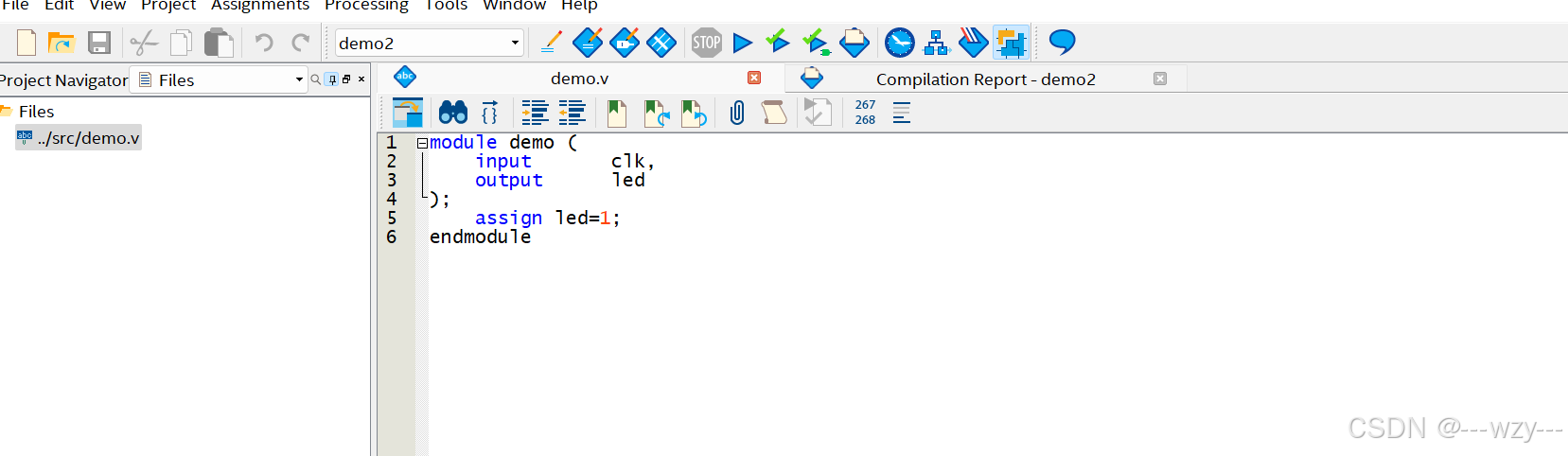

4.在src文件夹下写.v文件

// demo.v

module demo (

// 不写类型,默认wire型

input clk,

output led

);

// 让led是高电平工作

assign led=1;

endmodule5.启动文件

找寻.v文件

开始编译

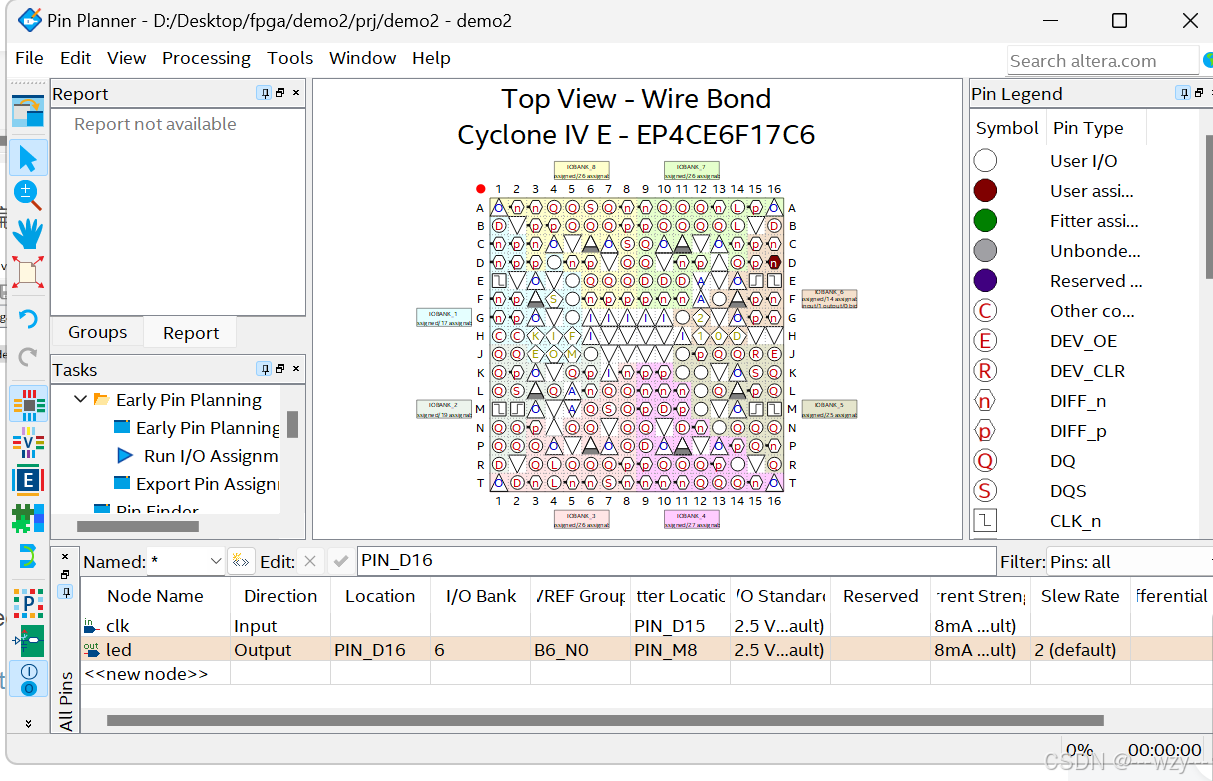

绑定led和引脚

重新编译

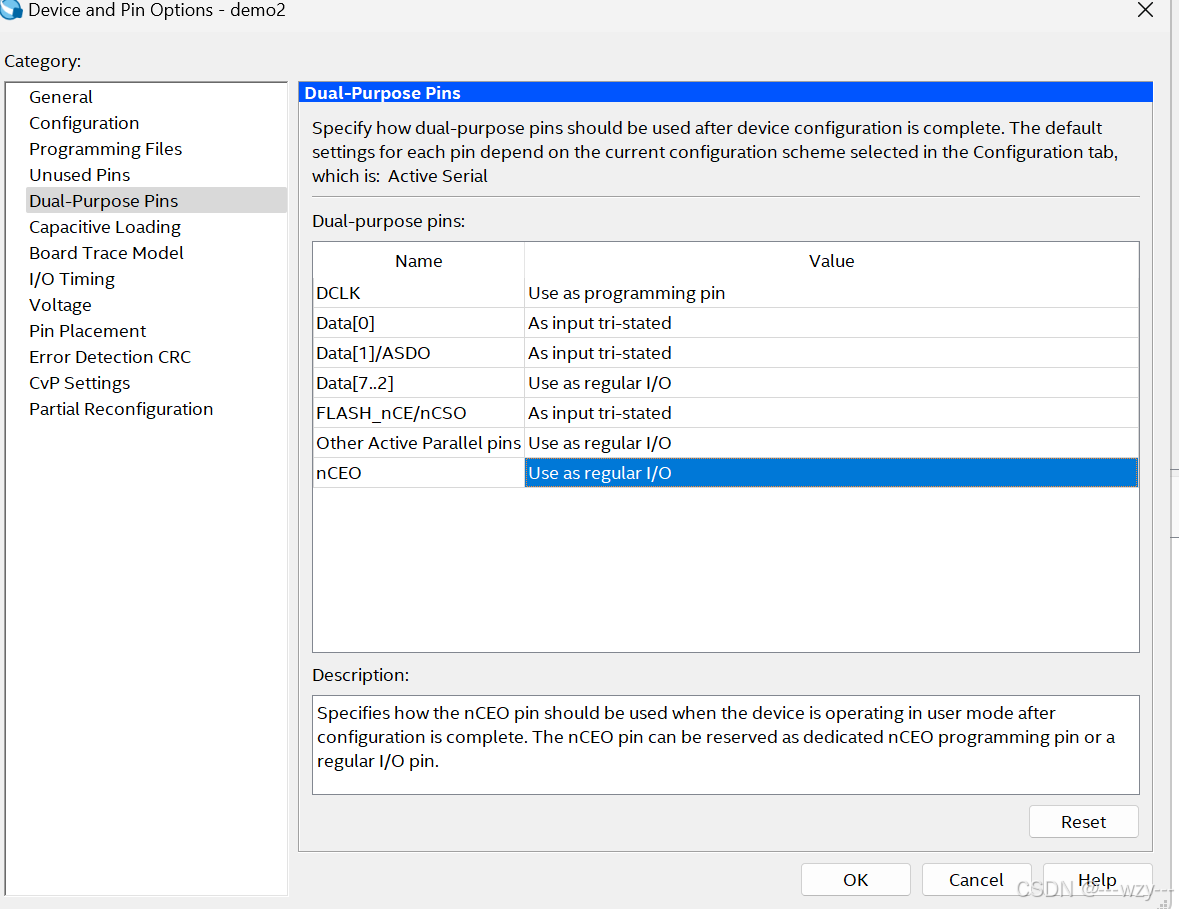

点击Device and Pin Options

点击Hardware Setup ,换成usb blaster

点击start启动

5.Verilog语法

常量说明:每一个变量的值就是0或者1

变量定义:

wire:在module中input和output后的变量默认是wire型

rag:如果在always中,才会使用rag

连续赋值:

assign:(主要用于组合逻辑电路)

always:(主要用于时序逻辑电路)

6.实例

启动一个灯

module demo (

input clk,

output led

);

assign led=1;

endmodule启动多个灯

module demo (

input clk,

output [3:0] led

);

assign led=4'b1010;

endmodule流水灯

/*

assign,always都是同时进行的

*/

module demo (

input clk,

input rst_n, // 复位

output reg [3:0] led

);

// 开始

wire add_cnt_500ms;

assign add_cnt_500ms=1'b1;

// 结束

wire end_cnt_500ms;

reg [24:0] cnt_500ms;

assign end_cnt_500ms=add_cnt_500ms&&(cnt_500ms==25_000_000-1);

// 计数

always @(posedge clk or negedge rst_n) begin

// 刚开始才会执行该if

if(!rst_n)begin

cnt_500ms<=0;

end

else if(add_cnt_500ms)begin

if(end_cnt_500ms)begin

cnt_500ms<=0;

end

else begin

cnt_500ms<=cnt_500ms+1;

end

end

end

// 跳灯(移位实现)

// always @(posedge clk or negedge rst_n) begin

// if(!rst_n) begin

// led=4'b1000

// end

// else if(led==4'b0001)begin

// led<=4'b1000

// end

// else if(end_cnt_500ms) begin

// led<=(led>>1)

// end

// end

// 挑灯(拼接实现)

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

led<=4'b1000;

end

else if(end_cnt_500ms)begin

led<={led[0],led[3:1]};

end

end

endmodule使用蜂鸣灯演奏两只老虎

module music(

input clk,

input rst_n,

output reg buzzer

);

//****************************************************//

//计数器1产生音符

//!开始条件

wire add_cnt_get;

assign add_cnt_get = 1'b1;

//!结束条件

wire end_cnt_get;

reg [17:0] cnt_get;//满足最大值25_000_000

reg [17:0] CNT_MAX;

assign end_cnt_get = add_cnt_get && (cnt_get == CNT_MAX - 1);

//!正常计数

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_get <= 0;//时序逻辑用非阻塞

end

else if(add_cnt_get)begin

if(end_cnt_get)begin//情况少的:清零

cnt_get <= 0;

end

else begin//情况多的:正常+1

cnt_get <= cnt_get + 1;

end

end

end

//****************************************************//

//计数器2音符

//!开始条件

wire add_cnt_repeat;

assign add_cnt_repeat = end_cnt_get;

//!结束条件

wire end_cnt_repeat;

reg [7:0] cnt_repeat;//满足最大值200

// wire [17:0] CNT_MAX;

assign end_cnt_repeat = add_cnt_repeat && (cnt_repeat == 200 - 1);

//!正常计数

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_repeat <= 0;//时序逻辑用非阻塞

end

else if(add_cnt_repeat)begin

if(end_cnt_repeat)begin//情况少的:清零

cnt_repeat <= 0;

end

else begin//情况多的:正常+1

cnt_repeat <= cnt_repeat + 1;

end

end

end

//****************************************************//

//计数器3切换音符

//!开始条件

wire add_cnt_change;

assign add_cnt_change = end_cnt_repeat;

//!结束条件

wire end_cnt_change;

reg [5:0] cnt_change;//满足最大值48

// wire [17:0] CNT_MAX;

assign end_cnt_change = add_cnt_change && (cnt_change == 48 - 1);

//!正常计数

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_change <= 0;//时序逻辑用非阻塞

end

else if(add_cnt_change)begin

if(end_cnt_change)begin//情况少的:清零

cnt_change <= 0;

end

else begin//情况多的:正常+1

cnt_change <= cnt_change + 1;

end

end

end

parameter

M_1Do = 95600,

M_2Re = 85150,

M_3Mi = 75850,

M_4Fa = 71600,

M_5So = 63750,

M_6La = 56800,

L_5So = 127550;

always @(*) begin

case (cnt_change)

6'd0 : CNT_MAX = M_1Do;

6'd1 : CNT_MAX = M_2Re;

6'd2 : CNT_MAX = M_3Mi;

6'd3 : CNT_MAX = M_1Do;

6'd4 : CNT_MAX = M_2Re;

6'd5 : CNT_MAX = M_3Mi;

6'd6 : CNT_MAX = M_1Do;

6'd7 : CNT_MAX = M_3Mi;

6'd8 : CNT_MAX = M_4Fa;

6'd9 : CNT_MAX = M_5So;

6'd10 :CNT_MAX = M_5So;

6'd11 :CNT_MAX = M_3Mi;

6'd12 :CNT_MAX = M_4Fa;

6'd13 :CNT_MAX = M_5So;

6'd14 :CNT_MAX = M_5So;

6'd15 :CNT_MAX = M_5So;

6'd16 :CNT_MAX = M_6La;

6'd17 :CNT_MAX = M_5So;

6'd18 :CNT_MAX = M_4Fa;

6'd19 :CNT_MAX = M_3Mi;

6'd20 :CNT_MAX = M_3Mi;

6'd21 :CNT_MAX = M_1Do;

6'd22 :CNT_MAX = M_1Do;

6'd23 :CNT_MAX = M_5So;

6'd24 :CNT_MAX = M_6La;

6'd25 :CNT_MAX = M_5So;

6'd26 :CNT_MAX = M_4Fa;

6'd27 :CNT_MAX = M_3Mi;

6'd28 :CNT_MAX = M_3Mi;

6'd29 :CNT_MAX = M_1Do;

6'd30 :CNT_MAX = M_1Do;

6'd31 :CNT_MAX = M_2Re;

6'd32 :CNT_MAX = M_2Re;

6'd33 :CNT_MAX = L_5So;

6'd34 :CNT_MAX = L_5So;

6'd35 :CNT_MAX = M_1Do;

6'd36 :CNT_MAX = M_1Do;

6'd37 :CNT_MAX = 1;

6'd38 :CNT_MAX = 1;

6'd39 :CNT_MAX = M_2Re;

6'd40 :CNT_MAX = M_2Re;

6'd41 :CNT_MAX = L_5So;

6'd42 :CNT_MAX = L_5So;

6'd43 :CNT_MAX = M_1Do;

6'd44 :CNT_MAX = M_1Do;

6'd45 :CNT_MAX = 1;

6'd46 :CNT_MAX = 1;

6'd47 :CNT_MAX = 1;

default: ;//空语句

endcase

end

//描述输出的信号

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

buzzer <= 1;

end

else if(cnt_get > (CNT_MAX >> 1))begin

buzzer <= 0;

end

else begin

buzzer <= 1;

end

end

endmodule

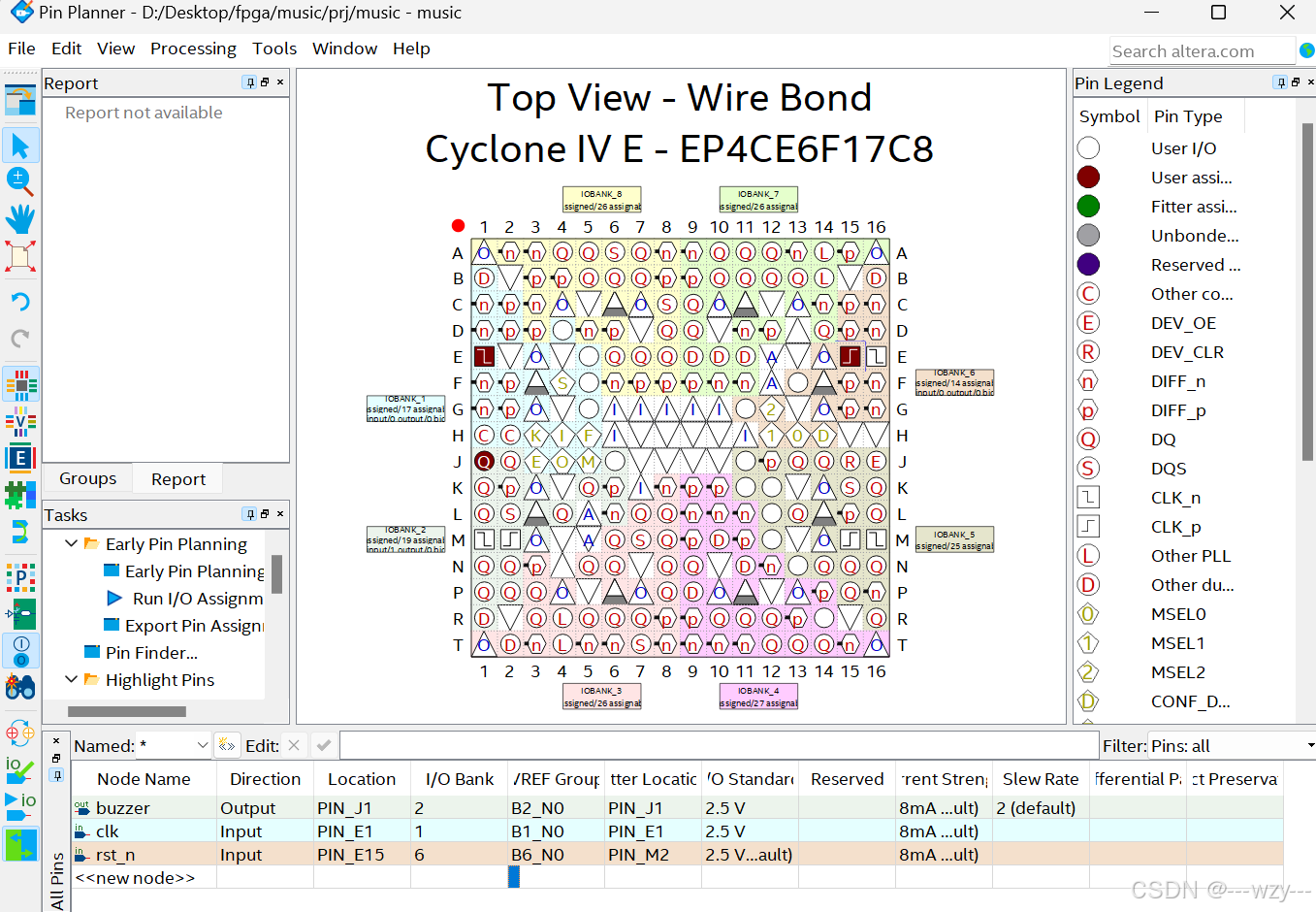

引脚绑定