一、问题出现场景:

原理可以参考链接:SPI协议详解(图文并茂+超详细) - 知乎 (zhihu.com)

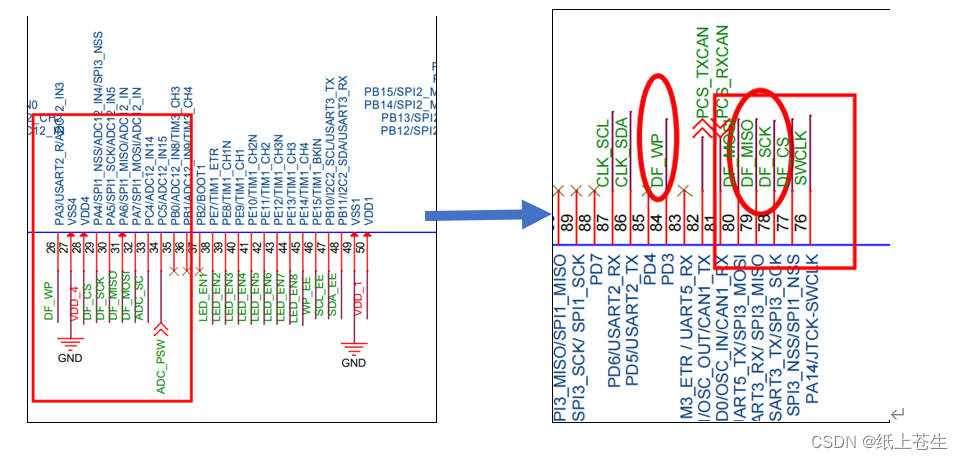

1.SPI的引脚变动

二、程序内部移植注意

移植已有项目的SPI程序架构

以上引脚变动需要注意的点:

1.引脚使用的变动,比如从PA3变为PB4

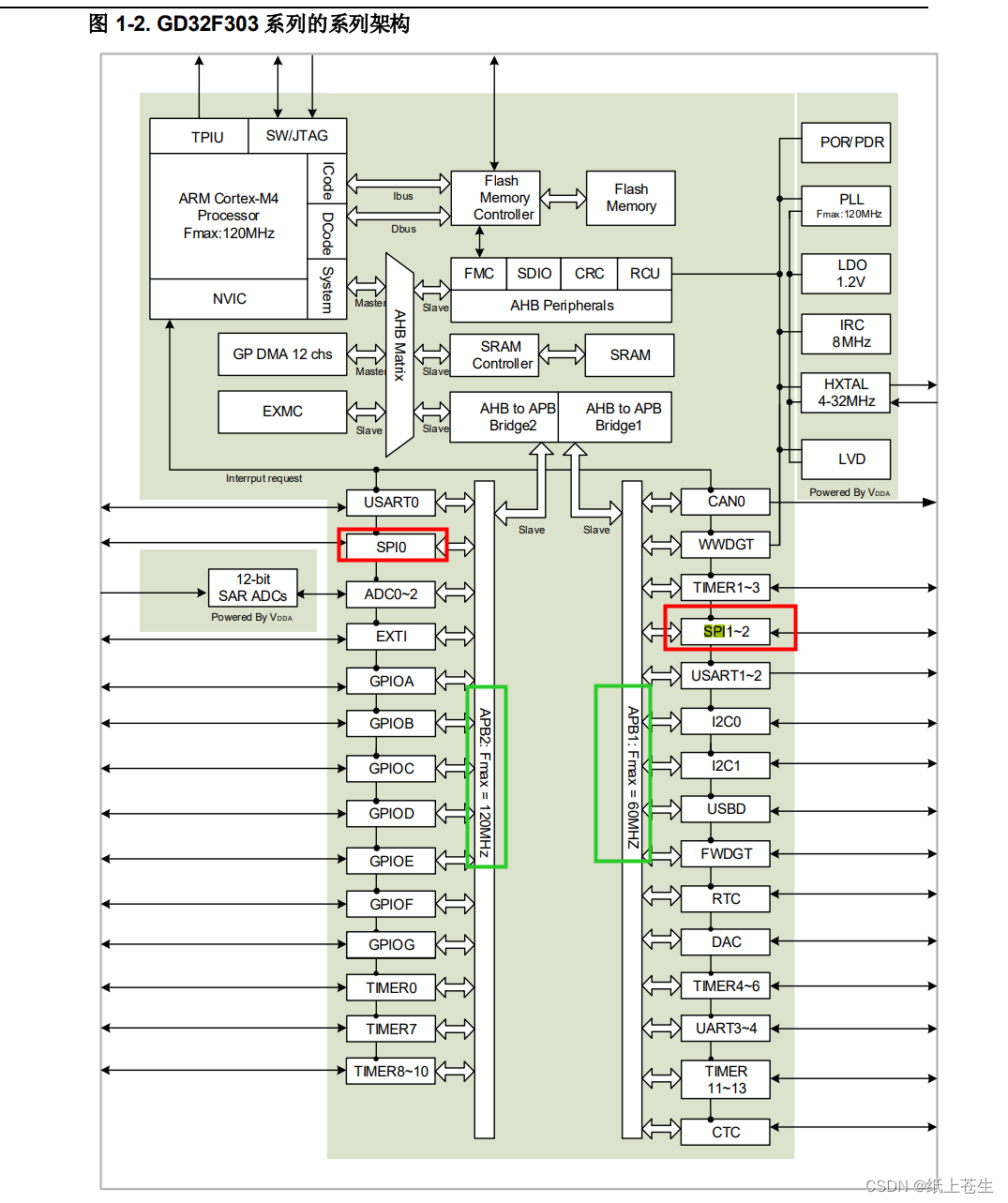

2.SPI编号的变动,有的MCU可能会有三组SPI【SPI1 SPI2 SPI3】

3.SPI的时钟源是否变化,这个决定SPI 的时钟频率,正常频率设置应该为 总线/2

【原来SPI1 SPI_PSC_8】

/* SPI2 parameter config */

spi_init_struct.trans_mode = SPI_TRANSMODE_FULLDUPLEX;

spi_init_struct.device_mode = SPI_MASTER;

spi_init_struct.frame_size = SPI_FRAMESIZE_8BIT;

spi_init_struct.clock_polarity_phase = SPI_CK_PL_LOW_PH_1EDGE;

spi_init_struct.nss = SPI_NSS_SOFT;

spi_init_struct.prescale = SPI_PSC_16 ;

spi_init_struct.endian = SPI_ENDIAN_MSB;

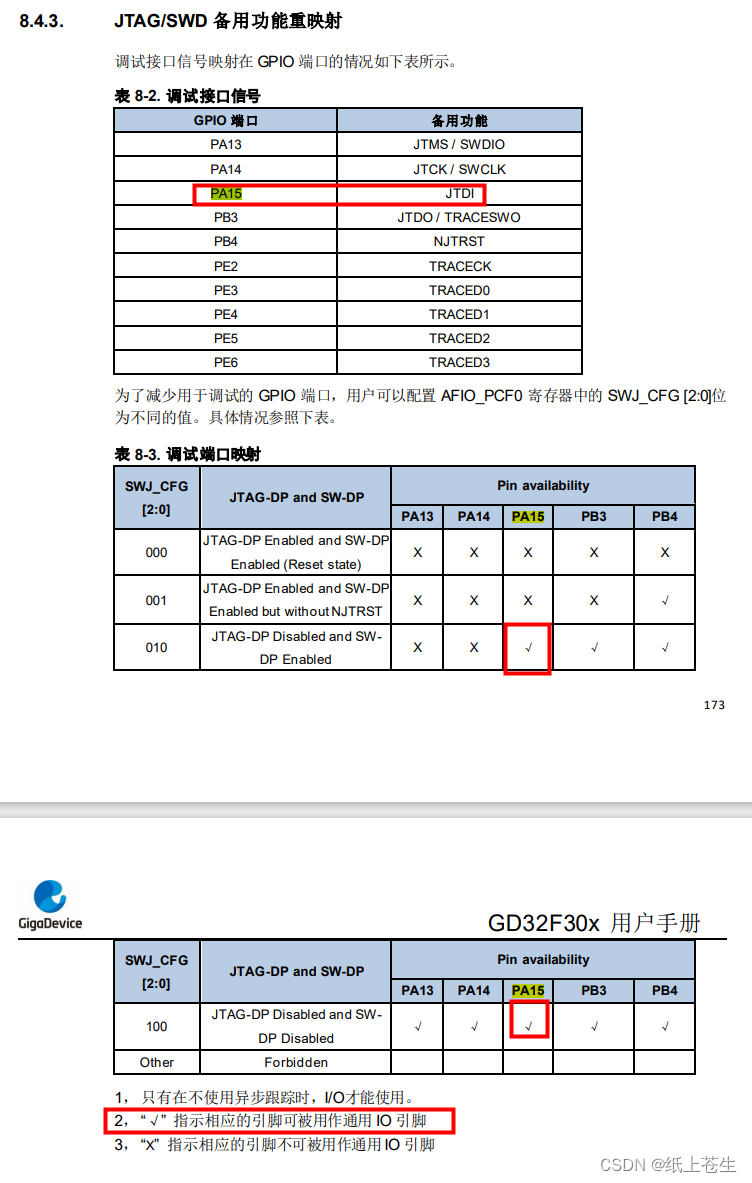

spi_init(SPI2, &spi_init_struct);4.引脚变动时需要查看芯片手册,确认变动的引脚是否是特殊引脚

PA15为特殊引脚需要做重映射

void gpio_config(void)

{ /* GPIO output */

gpio_pin_remap_config(GPIO_SWJ_SWDPENABLE_REMAP,ENABLE);

gpio_pin_remap_config(GPIO_SPI2_REMAP, ENABLE);

}三、波形分析问题点

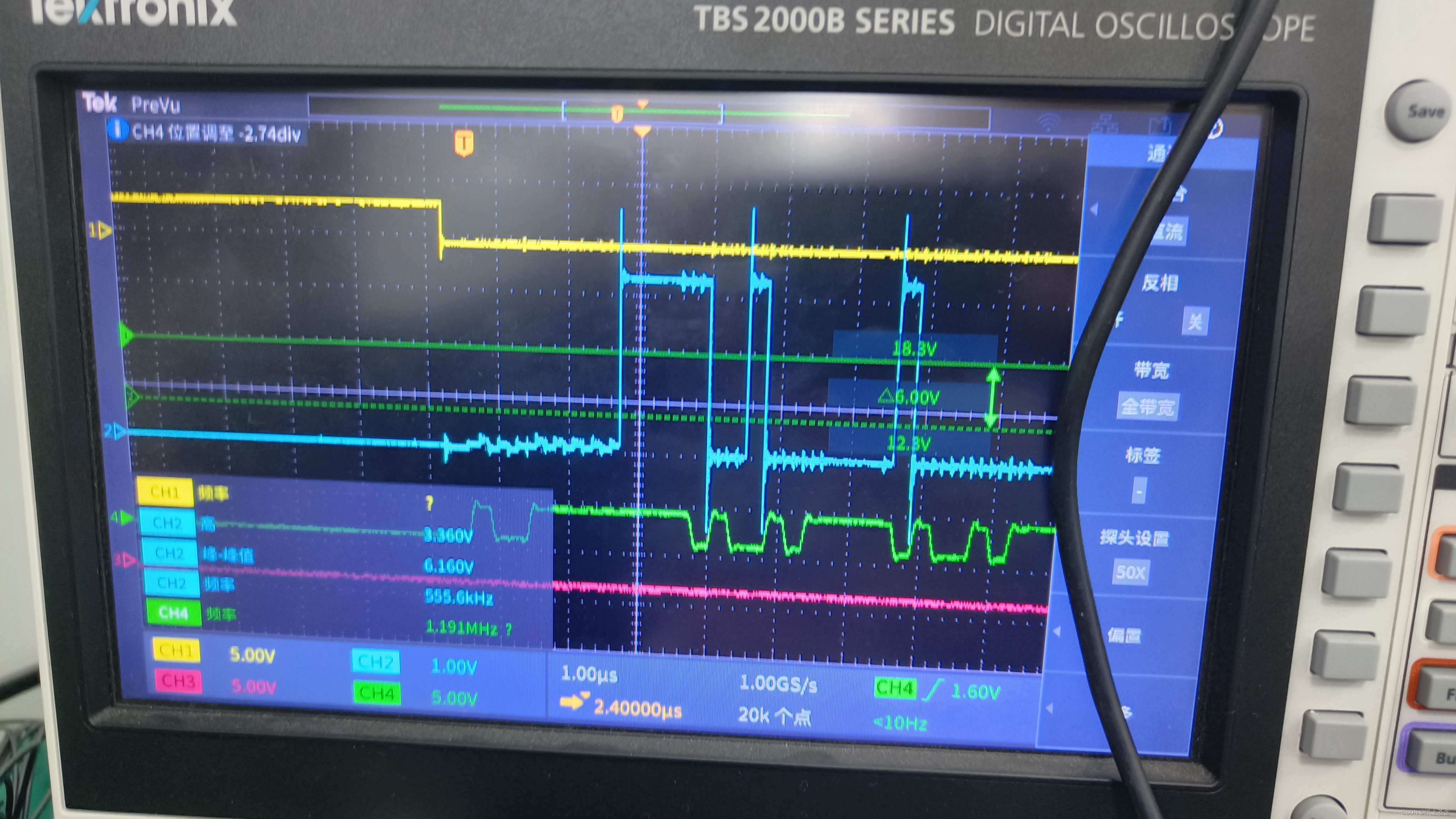

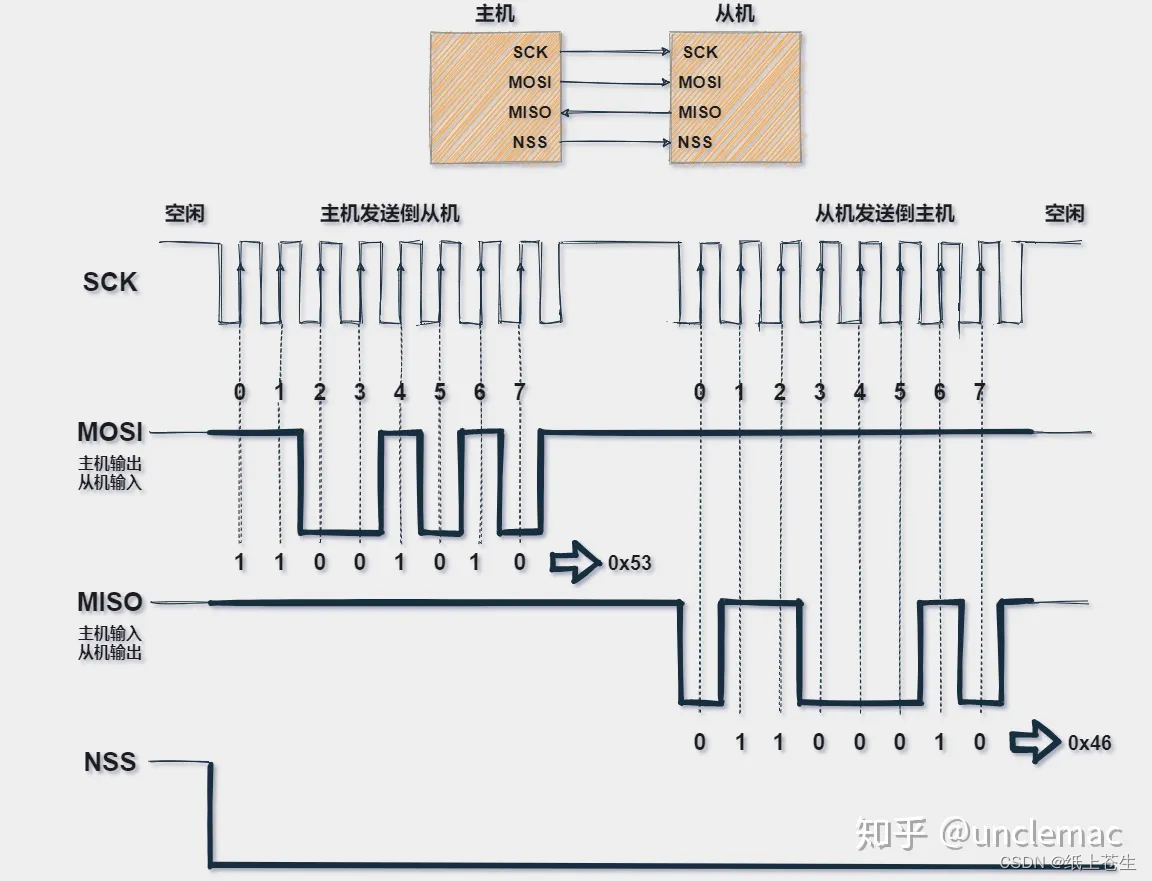

波形分析思路:

1.CS引脚是否可以顺利的拉高拉低

2.主机发送数据时波形是否正确

3.从机发送数据时波形是否正确

- 连接SPI的引脚到示波器对应的通道

- 使用示波器抓捕波形

- 进入程序进行DEG

实际波形可以参考下图:

参考链接:SPI协议详解(图文并茂+超详细) - 知乎 (zhihu.com)

【SPI有四种模式,由极性和相序决定】

四、出现该问题的反思

1.对于芯片底层配置不熟悉

主要时芯片手册的了解和引脚配置的知识存在盲区

很多引脚配置最好参考原厂配置,【这里上传了GD的资料】

2.对于SPI出现问题解决思路不清晰

检查引脚配置

检查时钟源

检查波形

3.对于时钟的概念和意义未深刻理解

【待补充,这里就总结一下SPI调试过程中的收获】