不想手操一遍的拉到最下面直接从百度网盘链接获取

软件是Quartus II 18.0,该实验使用DE2-115开发板,fpga芯片为cyclone IV EP4CE115F29C7。

软件可以在微信公众号-软件管家中下载。

实验现象

通过设置四个界面:时钟,计时器,闹钟,设置时钟并且都可以对他们时分秒位进行设置,闹钟现象为红灯闪烁。(具体的实现出来自己通过引脚图找到那几个按键和拨码开关对应代码自己玩一下)

顶层模块clock

/*

mode (按下mooe按键+1)

0 显示

小时:0-23

分钟:0-59

秒:0-59

1 计时

分钟:秒:99

start-->开始计时(1)-->暂停计时(0)-->开始计时...

reset-归零

2 闹钟设置

start--加1(默认分钟)

reset--切换小时/分钟设置 默认分钟-->小时-->分钟

小时:0-23

分钟:0-59

3 时间设置

start--

秒(默认)-->归0

分钟/小时-->+1

reset-->

秒-->分钟-->小时

*/

module clock

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

input wire light_an , //控制亮度

input wire mooe_an , //功能按键

input wire start_an , //调整数值按键

input wire reset_an , //切换区域按键

output reg led , //做闹钟用 LEDR0 闪烁

output reg [3:0] led_mode , //显示当前模式 LEDR17-LEDR14

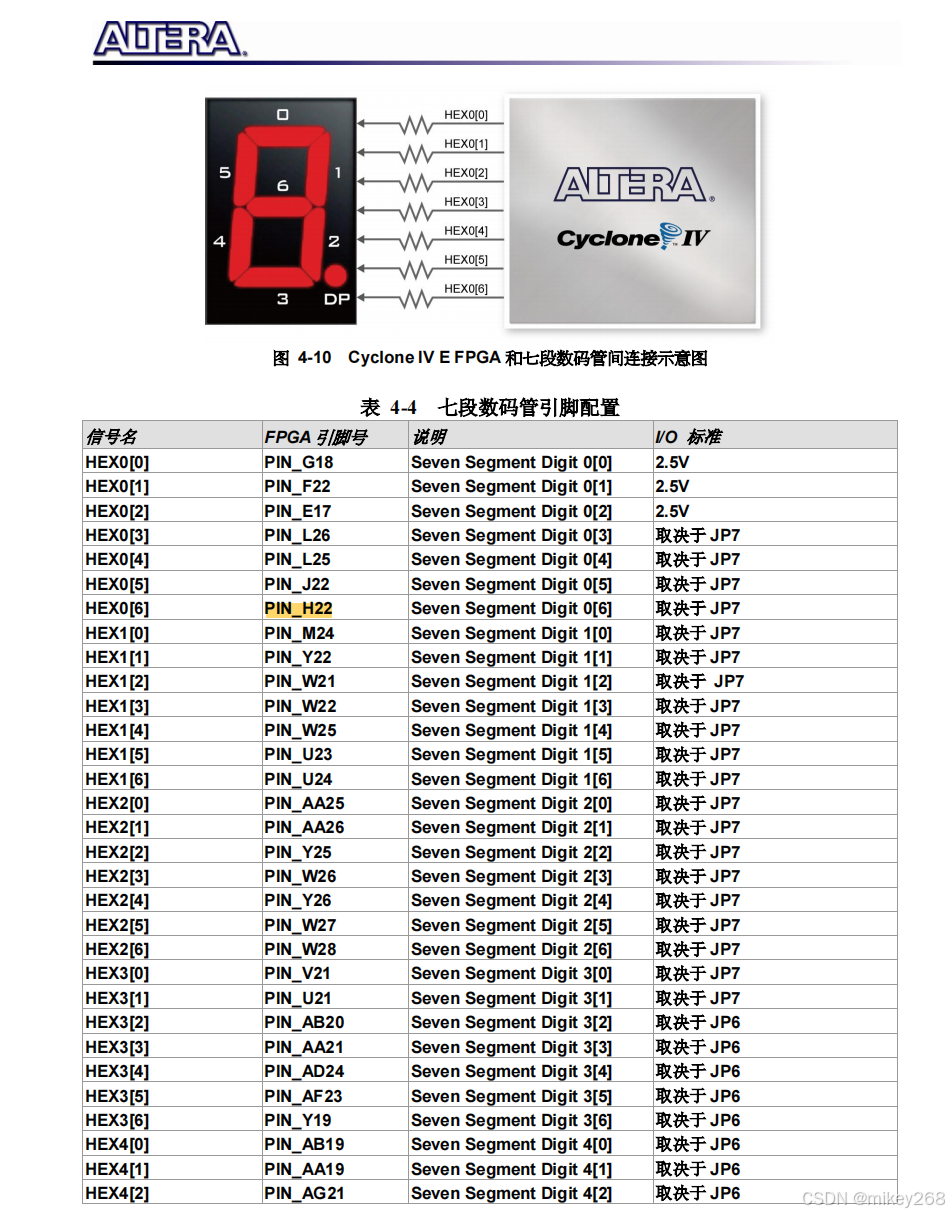

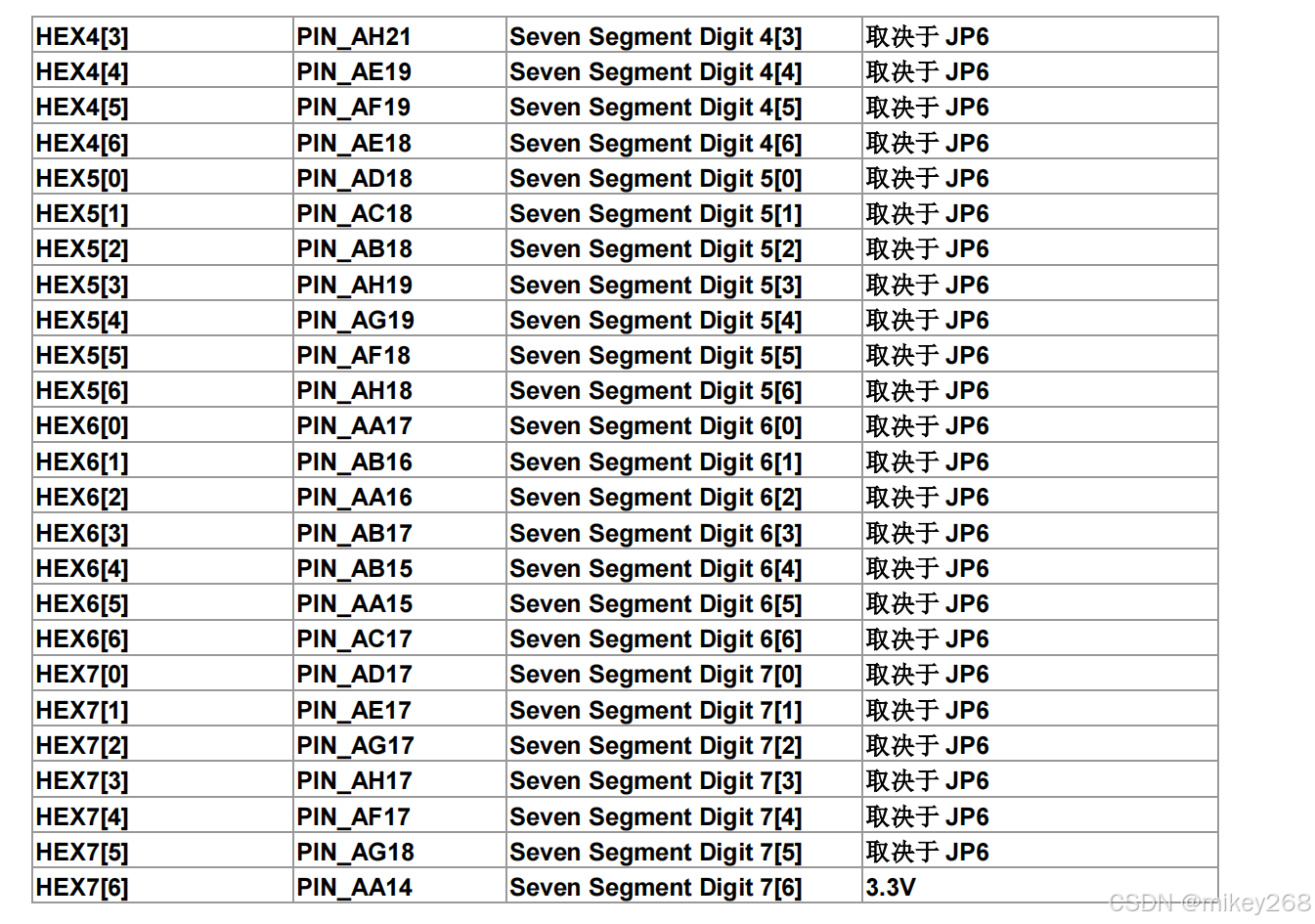

output wire [6:0] SG0,SG1,SG2,SG3,SG4,SG5,SG6,SG7 //数码管的值 7-6,4-3,1-0显示数字 5,2显示:

);

reg [1:0] mode;//模式, mooe按键控制

wire light,mooe,start,reset; //按键脉冲,高电平有效

wire clk1s_flag,clk10ms_flag; //时钟标志位

wire [7:0] sec,min,hour; //时钟变量寄存

wire [7:0] min_keti,sec_keti,misec_keti;//计时变量寄存

wire [7:0] min_alarm,hour_alarm ; //闹钟变量寄存

//1s,10ms时钟产生模块

clock_generation clk_inst

(

.sys_clk (sys_clk ) , //系统时钟50MHZ

.sys_rst_n (sys_rst_n ) , //复位

.clock_generation1s_flag (clk1s_flag ) , //1s时钟脉冲标志位

.clock_generation10ms_flag (clk10ms_flag ) //10ms时钟脉冲标志位

);

//mode改变

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

mode <= 2'd0;

else if(mooe && (mode == 2'd3))

mode <= 2'd0;

else if(mooe)

mode <= mode + 1'd1;

else

mode <= mode;

//led_mode-显示当前模式

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

led_mode <= 4'b0000;

else

case(mode)

0:led_mode <= 4'b1000;

1:led_mode <= 4'b0100;

2:led_mode <= 4'b0010;

3:led_mode <= 4'b0001;

default: led_mode <= 4'b1000;

endcase

//0.显示功能+ 3.时间设置

clock_display clockdisplay_inst

(

.sys_clk (sys_clk ) , //系统时钟50MHZ

.sys_rst_n (sys_rst_n ) , //复位

.mode (mode ) , //模式-相当于使能

.clk1s_flag(clk1s_flag ) , //1s脉冲

.mooe (mooe ) , //调整功能按键

.start (start ) , //开始暂停计数

.reset (reset ) , //置0

.sec_out (sec ) , //显示-秒

.min_out (min ) , //显示-分钟

.hour_out (hour ) //显示-小时

);

//1.计数功能

keeptime keeptime_inst

(

.sys_clk (sys_clk ) , //系统时钟50MHZ

.sys_rst_n (sys_rst_n ) , //复位

.mode (mode ) , //模式-相当于使能

.clk10ms_flag (clk10ms_flag ) , //10ms脉冲

.mooe (mooe ) , //调整功能按键

.start (start ) , //开始暂停计数

.reset (reset ) , //置0

.min_keti (min_keti ) , //计时-分钟

.sec_keti (sec_keti ) , //计时-秒

.misec_keti (misec_keti ) //计时-10ms

);

//2.闹钟调整

alarmclock alarmclock_inst

(

.sys_clk (sys_clk ) , //系统时钟50MHZ

.sys_rst_n (sys_rst_n ) , //复位

.mode (mode ) , //模式-相当于使能

.mooe (mooe ) , //调整功能按键

.start (start ) , //开始暂停计数

.reset (reset ) , //置0

.min_alarm (min_alarm ) , //闹钟-分钟

.hour_alarm(hour_alarm) //闹钟-小时

);

//闹钟报警-1分钟灯闪烁

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

led <= 1'b0;

else if(min != min_alarm || hour != hour_alarm)

led <= 1'b0;

else if((hour == hour_alarm) && (min == min_alarm) && clk1s_flag)

led <= ~led;

//数码管显示模块

digital_display digital_display_inst

(

.sys_clk (sys_clk ) , //系统时钟50MHZ

.sys_rst_n (sys_rst_n ) , //复位

.mode (mode ) , //模式-相当于使能

.light (light ) , //控制显示亮度

//时钟变量

.sec (sec ) ,

.min (min ) ,

.hour (hour ) ,

//计时变量

.min_keti (min_keti ) ,

.sec_keti (sec_keti ) ,

.misec_keti(misec_keti) ,

//闹钟变量

.min_alarm (min_alarm ) ,

.hour_alarm(hour_alarm) ,

//数码管的值 7-6,4-3,1-0显示数字 5,2显示:

.SG0 (SG0) ,

.SG1 (SG1) ,

.SG2 (SG2) ,

.SG3 (SG3) ,

.SG4 (SG4) ,

.SG5 (SG5) ,

.SG6 (SG6) ,

.SG7 (SG7)

);

//按键滤波器,按下按键产生一个高脉冲

key_filiter key_filiter_inst0

(

.sys_clk (sys_clk ) ,

.sys_rst_n(sys_rst_n) ,

.key_in (light_an) ,

.key_flag (light)

);

key_filiter key_filiter_inst1

(

.sys_clk (sys_clk ) ,

.sys_rst_n(sys_rst_n) ,

.key_in (mooe_an) ,

.key_flag (mooe)

);

key_filiter key_filiter_inst2

(

.sys_clk (sys_clk ) ,

.sys_rst_n(sys_rst_n) ,

.key_in (start_an) ,

.key_flag (start)

);

key_filiter key_filiter_inst3

(

.sys_clk (sys_clk ) ,

.sys_rst_n(sys_rst_n) ,

.key_in (reset_an) ,

.key_flag (reset)

);

endmodule

底层模块key_filiter

//按键滤波器,按下按钮后即低电平输入,经过该模块输出一个系统时钟周期的高脉冲

module key_filiter

(

input sys_clk ,

input sys_rst_n ,

input key_in ,

output reg key_flag

);

reg [19:0] cnt_20ms;

parameter CNT_MAX=20'd999999;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_20ms<=20'd0;

else if(key_in)

cnt_20ms<=20'd0;

else if(cnt_20ms==CNT_MAX) //最大值保持

cnt_20ms<=CNT_MAX;

else

cnt_20ms<=cnt_20ms+1'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

key_flag<=1'b0;

else if(cnt_20ms==CNT_MAX-20'd1)

key_flag<=1'b1;

else

key_flag<=1'b0;

endmodule

底层模块clock_generation

//1s,10ms时钟产生模块

module clock_generation

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

output reg clock_generation1s_flag , //1s时钟脉冲标志位

output reg clock_generation10ms_flag //10ms时钟脉冲标志位

);

parameter CNT_MAX_1S = 28'd49_999_999;

parameter CNT_MAX_10MS = 20'd499_999;

reg [27:0] clock_generation_1s ;

reg [19:0] clock_generation_10ms ;

//1s时钟脉冲产生

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clock_generation_1s <= 28'd0;

else if(clock_generation_1s == CNT_MAX_1S)

clock_generation_1s <= 28'd0;

else

clock_generation_1s <= clock_generation_1s + 1'd1;

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clock_generation1s_flag <= 1'b0;

else if(clock_generation_1s == CNT_MAX_1S-1)

clock_generation1s_flag <= 1'b1;

else

clock_generation1s_flag <= 1'b0;

//10ms时钟脉冲产生

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clock_generation_10ms <= 20'd0;

else if(clock_generation_10ms == CNT_MAX_10MS)

clock_generation_10ms <= 20'd0;

else

clock_generation_10ms <= clock_generation_10ms + 1'd1;

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

clock_generation10ms_flag <= 1'b0;

else if(clock_generation_10ms == CNT_MAX_10MS-1)

clock_generation10ms_flag <= 1'b1;

else

clock_generation10ms_flag <= 1'b0;

endmodule

底层模块clock_display

/*

0 显示

小时:0-23

分钟:0-59

秒:0-59

3 时间设置

start--

秒(默认)-->归0

分钟/小时-->+1

reset-->

秒-->分钟-->小时

mode-->返回时间显示(按过start,reset)

*/

module clock_display

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

input wire [1:0] mode , //模式-相当于使能

input wire clk1s_flag , //1s脉冲

input wire mooe , //调整功能按键

input wire start , //开始暂停计数

input wire reset , //调整位置

output reg [7:0] sec_out , //显示-秒

output reg [7:0] min_out , //显示-分钟

output reg [7:0] hour_out //显示-小时

);

reg [1:0] position;//调整数据位置

//position;调整数据位置 0-秒,1-分,2-时

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

position <= 2'd0;

else if(mode != 2'd3)

position <= 2'd0;

else if((mode == 2'd3) && reset && (position == 2'd2))

position <= 2'd0;

else if((mode == 2'd3) && reset) //每按下一次reset建位置更改一次

position <= position + 1'd1;

//秒产生

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

sec_out <= 8'd50;

else if((mode != 2'd3) && clk1s_flag && (sec_out == 8'd59))

sec_out <= 8'd0;

else if((mode != 2'd3) && clk1s_flag) //秒产生

sec_out <= sec_out + 1'd1;

//mode == 2'd3

else if((mode == 2'd3) && (position == 2'd0) && start) //mode==3即时间设置,按下start秒清0

sec_out <= 8'd0;

//分产生

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

min_out <= 8'd59;

else if((mode != 2'd3) && clk1s_flag && (min_out == 8'd59) && (sec_out == 8'd59))

min_out <= 8'd0;

else if((mode != 2'd3) && clk1s_flag && (sec_out == 8'd59)) //分产生

min_out <= min_out + 1'd1;

//mode == 2'd3

else if((mode == 2'd3) && (position == 2'd1) && start && (min_out == 8'd59)) //分钟==59,按下start秒分清0

min_out <= 8'd0;

else if((mode == 2'd3) && (position == 2'd1) && start) //mode==3即时间设置,按下start分加一

min_out <= min_out + 1'd1;

//时产生

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

hour_out <= 8'd23;

else if((mode != 2'd3) && clk1s_flag && (hour_out == 8'd23) && (min_out == 8'd59) && (sec_out == 8'd59))

hour_out <= 8'd0;

else if((mode != 2'd3) && clk1s_flag && (min_out == 8'd59) && (sec_out == 8'd59))

hour_out <= hour_out + 1'd1;

//mode == 2'd3

else if((mode == 2'd3) && (position == 2'd1) && start && (hour_out == 8'd23) && (min_out == 8'd59)) //分钟溢出且小时==23,时清0

hour_out <= 8'd0;

else if((mode == 2'd3) && (position == 2'd2) && start && (hour_out == 8'd23)) //小时==23,按下start秒时清0

hour_out <= 8'd0;

else if((mode == 2'd3) && (position == 2'd2) && start) //mode==3即时间设置,按下start时加一

hour_out <= hour_out + 1'd1;

endmodule

底层模块keeptime

/*

mooe

1 计时

分钟:秒:99

start-->开始计时(1)-->暂停计时(0)-->开始计时...

reset-归零

//mode-->返回时间显示(按过start,reset)

*/

module keeptime

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

input wire [1:0] mode , //模式-相当于使能

input wire clk10ms_flag , //10ms脉冲

input wire mooe , //调整功能按键

input wire start , //开始暂停计数

input wire reset , //置0

output reg [7:0] min_keti , //计时-分钟

output reg [7:0] sec_keti , //计时-秒

output reg [7:0] misec_keti //计时-10ms

);

reg keeptime_flag;//控制计数启动暂停变量

//keeptime_flag;//控制计数启动暂停变量 0-停止/暂停,1-启动

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

keeptime_flag <= 1'b0;

else if(mode != 2'd1)

keeptime_flag <= 1'b0;

else if((mode == 2'd1) && start)

keeptime_flag <= ~keeptime_flag;

else if((mode == 2'd1) && reset)

keeptime_flag <= 1'b0;

//misec_keti 计时-10ms

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

misec_keti <= 8'd0;

else if(mode != 2'd1)

misec_keti <= 8'd0;

else if(reset || (mode == 2'd1 && keeptime_flag && clk10ms_flag && misec_keti == 99)) //按下reset按键 或者 计满99 us清0

misec_keti <= 8'd0;

else if(mode == 2'd1 && keeptime_flag && clk10ms_flag) //keeptime_flag==1,启动计时

misec_keti <= misec_keti + 1'd1;

//sec_keti 计时-秒

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

sec_keti <= 8'd0;

else if(mode != 2'd1)

sec_keti <= 8'd0;

else if(reset || (mode == 2'd1 && keeptime_flag && clk10ms_flag && sec_keti == 59)) //按下reset按键 或者 计满59 s清0

sec_keti <= 8'd0;

else if(mode == 2'd1 && keeptime_flag && clk10ms_flag && misec_keti == 99) //keeptime_flag==1,misec_keti溢出sec_keti++

sec_keti <= sec_keti + 1'd1;

//min_keti 计时-分钟

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

min_keti <= 8'd0;

else if(mode != 2'd1)

min_keti <= 8'd0;

else if(reset || (mode == 2'd1 && keeptime_flag && clk10ms_flag && min_keti == 59)) //按下reset按键 或者 计满59 分清0

min_keti <= 8'd0;

else if(mode == 2'd1 && keeptime_flag && clk10ms_flag && sec_keti == 59 && misec_keti == 99) //keeptime_flag==1,misec_keti溢出min_keti++

min_keti <= min_keti + 1'd1;

endmodule

底层模块alarmclock

/*

2 闹钟设置

start--加1(默认分钟)

reset--切换小时/分钟设置 默认分钟-->小时-->分钟

小时:0-23

分钟:0-59

mode-->返回时间显示(按过start,reset)

*/

module alarmclock

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

input wire [1:0] mode , //模式-相当于使能

input wire mooe , //调整功能按键

input wire start , //开始暂停计数

input wire reset , //置0

output reg [7:0] min_alarm , //闹钟-分钟

output reg [7:0] hour_alarm //闹钟-小时

);

reg position;//调整数据位置

//position;调整数据位置 0-分钟设置,1-小时设置

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

position <= 1'b0;

else if(mode != 2'd2)

position <= 1'b0;

else if(reset)

position <= ~position;

//min_alarm//闹钟-分钟

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

min_alarm <= 8'd0;

else if((mode == 2'd2) && (!position) && (start) && (min_alarm == 8'd59))//溢出清0

min_alarm <= 8'd0;

else if((mode == 2'd2) && (!position) && (start)) //mode == 2'd2,按下start键,闹钟-分钟+1

min_alarm <= min_alarm + 1'd1;

//hour_alarm//闹钟-小时

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

hour_alarm <= 8'd0;

else if((mode == 2'd2) && (!position) && (start) && (min_alarm == 8'd59) && (hour_alarm == 8'd23))//闹钟-分钟+1,且小时==23溢出清0

hour_alarm <= 8'd0;

else if((mode == 2'd2) && (position) && (start) && (hour_alarm == 8'd23)) //闹钟-小时+1,且小时==23溢出清0

hour_alarm <= 8'd0;

else if((mode == 2'd2) && (position) && (start)) //mode == 2'd2,按下start键,闹钟-小时+1

hour_alarm <= hour_alarm + 1'd1;

endmodule

底层模块digital_display

//数码管显示模块

module digital_display

(

input wire sys_clk , //系统时钟50MHZ

input wire sys_rst_n , //复位

input wire [1:0] mode , //模式-相当于使能

input wire light , //控制显示亮度

//时钟变量

input wire [7:0] sec ,

input wire [7:0] min ,

input wire [7:0] hour ,

//计时变量

input wire [7:0] min_keti ,

input wire [7:0] sec_keti ,

input wire [7:0] misec_keti ,

//闹钟变量

input wire [7:0] min_alarm ,

input wire [7:0] hour_alarm ,

output reg [6:0] SG0,SG1,SG2,SG3,SG4,SG5,SG6,SG7 //数码管的值 7-6,4-3,1-0显示数字 5,2显示:

);

parameter CNT_1US_MAX=6'd49; //1个时钟20ns,50个即1us

parameter CNT_1MS_MAX=10'd999; //计满1000个即1ms

parameter unit = 4'd5;

reg [9:0] tim;

reg [5:0] cnt_1us;

reg [9:0] cnt_1ms;

wire [3:0] sec_ten,sec_unit,min_ten,min_unit,hour_ten,hour_unit;//时钟变量显示

wire [3:0] minketi_ten,minketi_unit,secketi_ten,secketi_unit,misecketi_ten,misecketi_unit;//计数变量显示变量

wire [3:0] minalarm_ten,minalarm_unit,houralarm_ten,houralarm_unit;//闹钟变量显示变量

assign sec_ten=sec/10;assign sec_unit=sec%10;

assign min_ten=min/10;assign min_unit=min%10;

assign hour_ten=hour/10;assign hour_unit=hour%10;

assign minketi_ten=min_keti/10;assign minketi_unit=min_keti%10;

assign secketi_ten=sec_keti/10;assign secketi_unit=sec_keti%10;

assign misecketi_ten=misec_keti/10;assign misecketi_unit=misec_keti%10;

assign minalarm_ten=min_alarm/10;assign minalarm_unit=min_alarm%10;

assign houralarm_ten=hour_alarm/10;assign houralarm_unit=hour_alarm%10;

//1us脉冲产生

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_1us<=6'd0;

else if(cnt_1us==CNT_1US_MAX)

cnt_1us<=6'd0;

else

cnt_1us<=cnt_1us+6'd1;

//1ms脉冲产生

always@(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_1ms<=10'd0;

else if((cnt_1ms==CNT_1MS_MAX)&&(cnt_1us==CNT_1US_MAX))

cnt_1ms<=10'd0;

else if(cnt_1us==CNT_1US_MAX)

cnt_1ms<=cnt_1ms+10'd1;

else

cnt_1ms<=cnt_1ms;

//亮度变量调整

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

tim <= 10'd0;

else if(tim >= 10'd999)

tim <= 10'd0;

else if(light)

tim <= tim + 10'd200;

else

tim <= tim;

//数码管显示

always @(posedge sys_clk or negedge sys_rst_n)

if(!sys_rst_n)

begin

SG0 <= 7'b1111111;

SG1 <= 7'b1111111;

SG3 <= 7'b1111111;

SG4 <= 7'b1111111;

SG6 <= 7'b1111111;

SG7 <= 7'b1111111;

SG2 <= 7'b1111111;

SG5 <= 7'b1111111;

end

else if(cnt_1ms<=tim)

begin

SG0 <= 7'b1111111;

SG1 <= 7'b1111111;

SG3 <= 7'b1111111;

SG4 <= 7'b1111111;

SG6 <= 7'b1111111;

SG7 <= 7'b1111111;

SG2 <= 7'b1111111;

SG5 <= 7'b1111111;

end

else

begin

if(mode == 2'd0)//时钟显示

begin

SG2 <= 7'b0111111;

SG5 <= 7'b0111111;

case(sec_unit)

0:SG0<=7'b1000000; 1:SG0<=7'b1111001;

2:SG0<=7'b0100100; 3:SG0<=7'b0110000;

4:SG0<=7'b0011001; 5:SG0<=7'b0010010;

6:SG0<=7'b0000010; 7:SG0<=7'b1111000;

8:SG0<=7'b0000000; 9:SG0<=7'b0010000; //7段译码值

default: SG0 <= 7'b1111111;

endcase

case(sec_ten)

0:SG1<=7'b1000000; 1:SG1<=7'b1111001;

2:SG1<=7'b0100100; 3:SG1<=7'b0110000;

4:SG1<=7'b0011001; 5:SG1<=7'b0010010;

6:SG1<=7'b0000010; 7:SG1<=7'b1111000;

8:SG1<=7'b0000000; 9:SG1<=7'b0010000; //7段译码值

default: SG1 <= 7'b1111111;

endcase

case(min_unit)

0:SG3<=7'b1000000; 1:SG3<=7'b1111001;

2:SG3<=7'b0100100; 3:SG3<=7'b0110000;

4:SG3<=7'b0011001; 5:SG3<=7'b0010010;

6:SG3<=7'b0000010; 7:SG3<=7'b1111000;

8:SG3<=7'b0000000; 9:SG3<=7'b0010000; //7段译码值

default: SG3 <= 7'b1111111;

endcase

case(min_ten)

0:SG4<=7'b1000000; 1:SG4<=7'b1111001;

2:SG4<=7'b0100100; 3:SG4<=7'b0110000;

4:SG4<=7'b0011001; 5:SG4<=7'b0010010;

6:SG4<=7'b0000010; 7:SG4<=7'b1111000;

8:SG4<=7'b0000000; 9:SG4<=7'b0010000; //7段译码值

default: SG4 <= 7'b1111111;

endcase

case(hour_unit)

0:SG6<=7'b1000000; 1:SG6<=7'b1111001;

2:SG6<=7'b0100100; 3:SG6<=7'b0110000;

4:SG6<=7'b0011001; 5:SG6<=7'b0010010;

6:SG6<=7'b0000010; 7:SG6<=7'b1111000;

8:SG6<=7'b0000000; 9:SG6<=7'b0010000; //7段译码值

default: SG6 <= 7'b1111111;

endcase

case(hour_ten)

0:SG7<=7'b1000000; 1:SG7<=7'b1111001;

2:SG7<=7'b0100100; 3:SG7<=7'b0110000;

4:SG7<=7'b0011001; 5:SG7<=7'b0010010;

6:SG7<=7'b0000010; 7:SG7<=7'b1111000;

8:SG7<=7'b0000000; 9:SG7<=7'b0010000; //7段译码值

default: SG7 <= 7'b1111111;

endcase

end

else if(mode == 2'd1)//计时显示

begin

SG2 <= 7'b0111111;

SG5 <= 7'b0111111;

case(misecketi_unit)

0:SG0<=7'b1000000; 1:SG0<=7'b1111001;

2:SG0<=7'b0100100; 3:SG0<=7'b0110000;

4:SG0<=7'b0011001; 5:SG0<=7'b0010010;

6:SG0<=7'b0000010; 7:SG0<=7'b1111000;

8:SG0<=7'b0000000; 9:SG0<=7'b0010000; //7段译码值

default: SG0 <= 7'b1111111;

endcase

case(misecketi_ten)

0:SG1<=7'b1000000; 1:SG1<=7'b1111001;

2:SG1<=7'b0100100; 3:SG1<=7'b0110000;

4:SG1<=7'b0011001; 5:SG1<=7'b0010010;

6:SG1<=7'b0000010; 7:SG1<=7'b1111000;

8:SG1<=7'b0000000; 9:SG1<=7'b0010000; //7段译码值

default: SG1 <= 7'b1111111;

endcase

case(secketi_unit)

0:SG3<=7'b1000000; 1:SG3<=7'b1111001;

2:SG3<=7'b0100100; 3:SG3<=7'b0110000;

4:SG3<=7'b0011001; 5:SG3<=7'b0010010;

6:SG3<=7'b0000010; 7:SG3<=7'b1111000;

8:SG3<=7'b0000000; 9:SG3<=7'b0010000; //7段译码值

default: SG3 <= 7'b1111111;

endcase

case(secketi_ten)

0:SG4<=7'b1000000; 1:SG4<=7'b1111001;

2:SG4<=7'b0100100; 3:SG4<=7'b0110000;

4:SG4<=7'b0011001; 5:SG4<=7'b0010010;

6:SG4<=7'b0000010; 7:SG4<=7'b1111000;

8:SG4<=7'b0000000; 9:SG4<=7'b0010000; //7段译码值

default: SG4 <= 7'b1111111;

endcase

case(minketi_unit)

0:SG6<=7'b1000000; 1:SG6<=7'b1111001;

2:SG6<=7'b0100100; 3:SG6<=7'b0110000;

4:SG6<=7'b0011001; 5:SG6<=7'b0010010;

6:SG6<=7'b0000010; 7:SG6<=7'b1111000;

8:SG6<=7'b0000000; 9:SG6<=7'b0010000; //7段译码值

default: SG6 <= 7'b1111111;

endcase

case(minketi_ten)

0:SG7<=7'b1000000; 1:SG7<=7'b1111001;

2:SG7<=7'b0100100; 3:SG7<=7'b0110000;

4:SG7<=7'b0011001; 5:SG7<=7'b0010010;

6:SG7<=7'b0000010; 7:SG7<=7'b1111000;

8:SG7<=7'b0000000; 9:SG7<=7'b0010000; //7段译码值

default: SG7 <= 7'b1111111;

endcase

end

else if(mode == 2'd2)//闹钟设置显示

begin

SG0 <= 7'b1111111;

SG1 <= 7'b1111111;

SG2 <= 7'b1111111;

case(minalarm_unit)

0:SG3<=7'b1000000; 1:SG3<=7'b1111001;

2:SG3<=7'b0100100; 3:SG3<=7'b0110000;

4:SG3<=7'b0011001; 5:SG3<=7'b0010010;

6:SG3<=7'b0000010; 7:SG3<=7'b1111000;

8:SG3<=7'b0000000; 9:SG3<=7'b0010000; //7段译码值

default: SG3 <= 7'b1111111;

endcase

case(minalarm_ten)

0:SG4<=7'b1000000; 1:SG4<=7'b1111001;

2:SG4<=7'b0100100; 3:SG4<=7'b0110000;

4:SG4<=7'b0011001; 5:SG4<=7'b0010010;

6:SG4<=7'b0000010; 7:SG4<=7'b1111000;

8:SG4<=7'b0000000; 9:SG4<=7'b0010000; //7段译码值

default: SG4 <= 7'b1111111;

endcase

case(houralarm_unit)

0:SG6<=7'b1000000; 1:SG6<=7'b1111001;

2:SG6<=7'b0100100; 3:SG6<=7'b0110000;

4:SG6<=7'b0011001; 5:SG6<=7'b0010010;

6:SG6<=7'b0000010; 7:SG6<=7'b1111000;

8:SG6<=7'b0000000; 9:SG6<=7'b0010000; //7段译码值

default: SG6 <= 7'b1111111;

endcase

case(houralarm_ten)

0:SG7<=7'b1000000; 1:SG7<=7'b1111001;

2:SG7<=7'b0100100; 3:SG7<=7'b0110000;

4:SG7<=7'b0011001; 5:SG7<=7'b0010010;

6:SG7<=7'b0000010; 7:SG7<=7'b1111000;

8:SG7<=7'b0000000; 9:SG7<=7'b0010000; //7段译码值

default: SG7 <= 7'b1111111;

endcase

end

else if(mode == 2'd3)//时钟设置显示

begin

SG2 <= 7'b0111111;

SG5 <= 7'b0111111;

case(sec_unit)

0:SG0<=7'b1000000; 1:SG0<=7'b1111001;

2:SG0<=7'b0100100; 3:SG0<=7'b0110000;

4:SG0<=7'b0011001; 5:SG0<=7'b0010010;

6:SG0<=7'b0000010; 7:SG0<=7'b1111000;

8:SG0<=7'b0000000; 9:SG0<=7'b0010000; //7段译码值

default: SG0 <= 7'b1111111;

endcase

case(sec_ten)

0:SG1<=7'b1000000; 1:SG1<=7'b1111001;

2:SG1<=7'b0100100; 3:SG1<=7'b0110000;

4:SG1<=7'b0011001; 5:SG1<=7'b0010010;

6:SG1<=7'b0000010; 7:SG1<=7'b1111000;

8:SG1<=7'b0000000; 9:SG1<=7'b0010000; //7段译码值

default: SG1 <= 7'b1111111;

endcase

case(min_unit)

0:SG3<=7'b1000000; 1:SG3<=7'b1111001;

2:SG3<=7'b0100100; 3:SG3<=7'b0110000;

4:SG3<=7'b0011001; 5:SG3<=7'b0010010;

6:SG3<=7'b0000010; 7:SG3<=7'b1111000;

8:SG3<=7'b0000000; 9:SG3<=7'b0010000; //7段译码值

default: SG3 <= 7'b1111111;

endcase

case(min_ten)

0:SG4<=7'b1000000; 1:SG4<=7'b1111001;

2:SG4<=7'b0100100; 3:SG4<=7'b0110000;

4:SG4<=7'b0011001; 5:SG4<=7'b0010010;

6:SG4<=7'b0000010; 7:SG4<=7'b1111000;

8:SG4<=7'b0000000; 9:SG4<=7'b0010000; //7段译码值

default: SG4 <= 7'b1111111;

endcase

case(hour_unit)

0:SG6<=7'b1000000; 1:SG6<=7'b1111001;

2:SG6<=7'b0100100; 3:SG6<=7'b0110000;

4:SG6<=7'b0011001; 5:SG6<=7'b0010010;

6:SG6<=7'b0000010; 7:SG6<=7'b1111000;

8:SG6<=7'b0000000; 9:SG6<=7'b0010000; //7段译码值

default: SG6 <= 7'b1111111;

endcase

case(hour_ten)

0:SG7<=7'b1000000; 1:SG7<=7'b1111001;

2:SG7<=7'b0100100; 3:SG7<=7'b0110000;

4:SG7<=7'b0011001; 5:SG7<=7'b0010010;

6:SG7<=7'b0000010; 7:SG7<=7'b1111000;

8:SG7<=7'b0000000; 9:SG7<=7'b0010000; //7段译码值

default: SG7 <= 7'b1111111;

endcase

end

end

endmodule

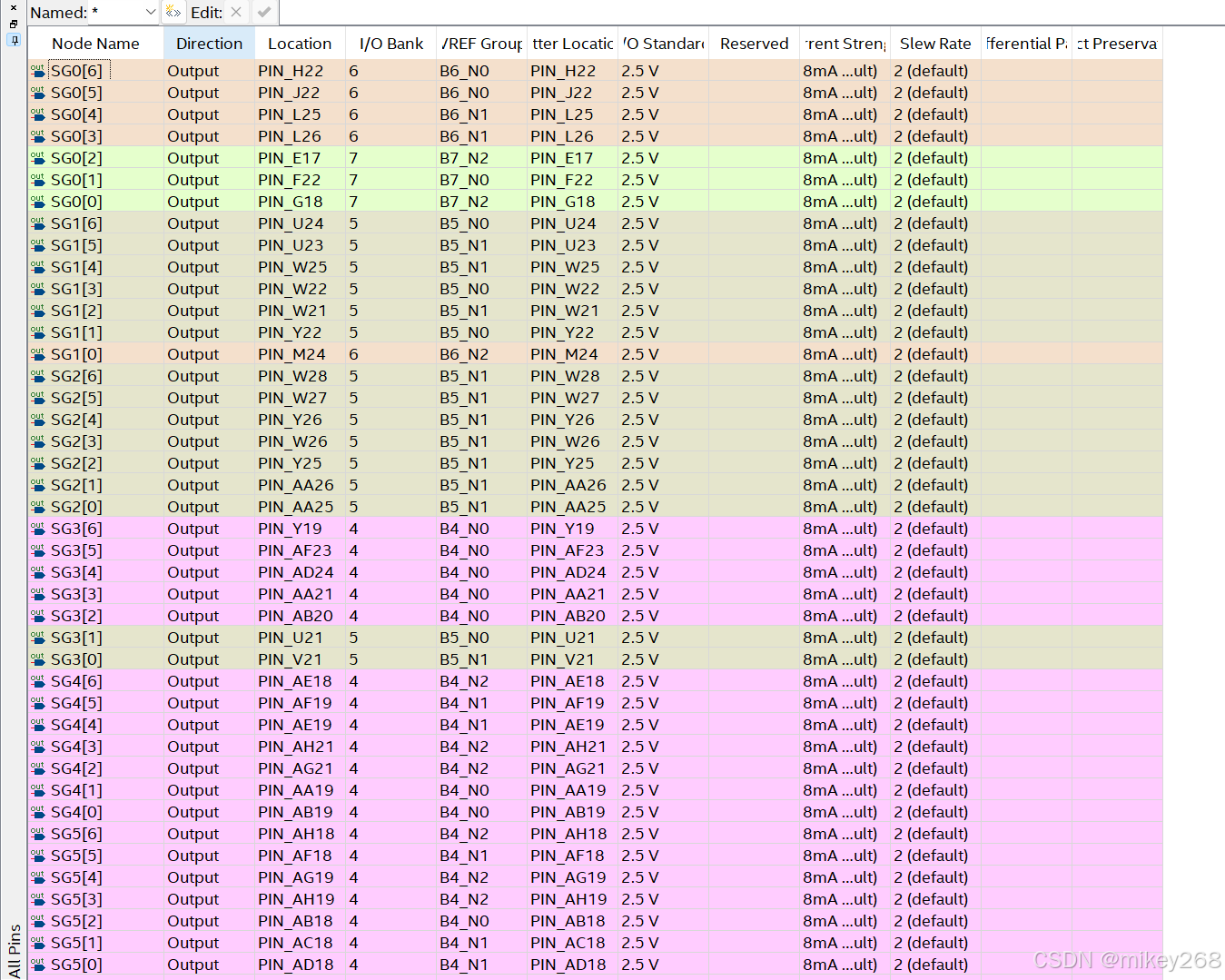

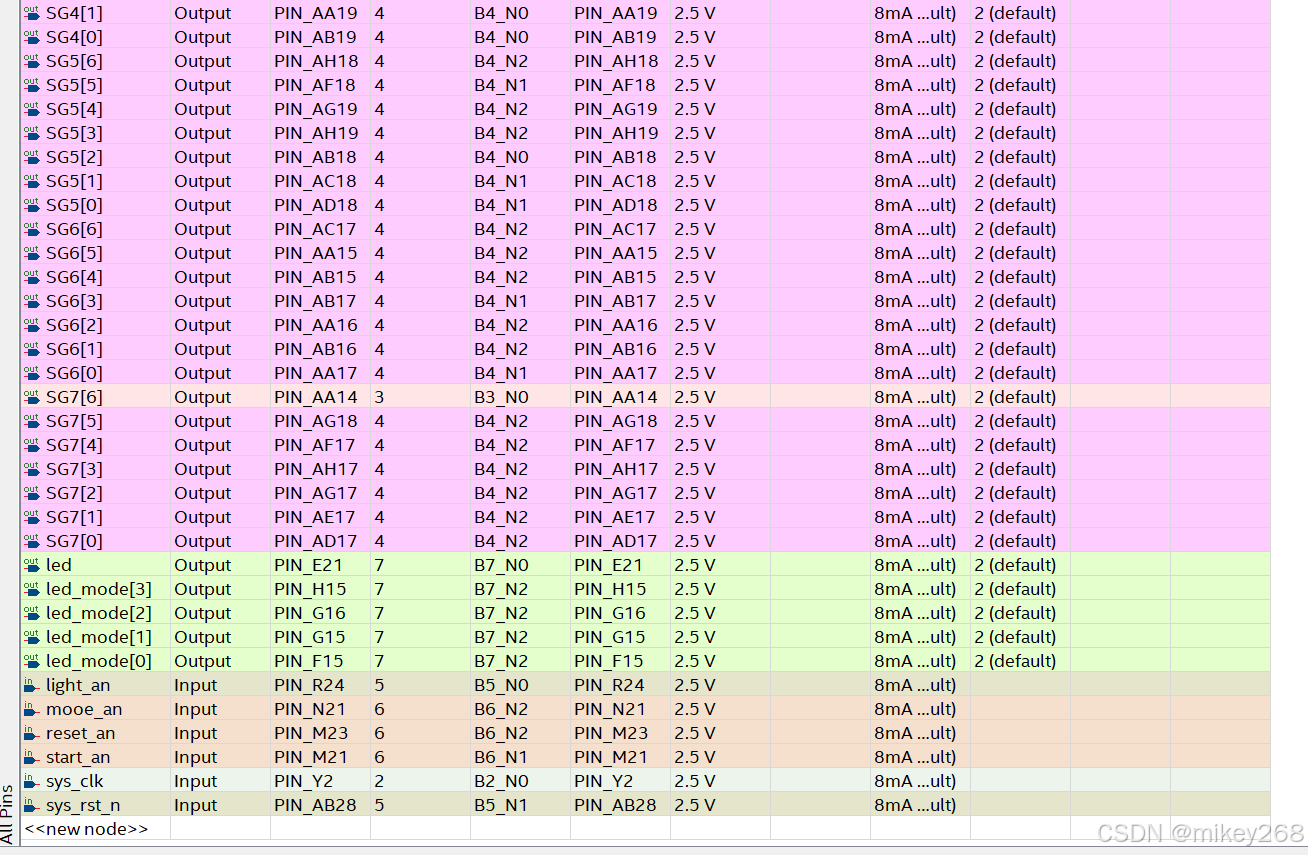

引脚配置(可以直接对着我配,有想法想换引脚可以对着下面的引脚图换)

数据手册查找相应引脚

拨码和按键开关对应引脚还有led引脚,时钟信号引脚等看上一篇博客

通过百度网盘分享的文件:clock.zip

链接:https://pan.baidu.com/s/182ty6Xf8jydXSD7f0sVBHA?pwd=1111

提取码:1111