实验目的

(1)学习组合电路的设计方法;

(2)了解译码器的工作原理和构成;

(3)熟悉 EDA 工具软件的使用方法。

实验设备及器件

(1)操作系统为 WINDOWS XP 的计算机一台;

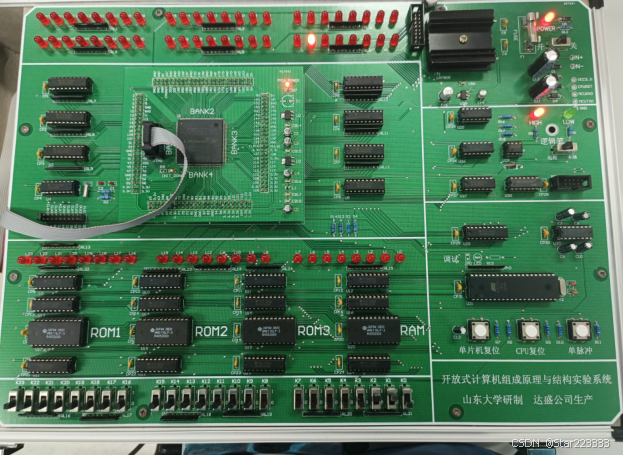

(2)数字逻辑与计算机组成原理实验系统一台;

(3)三输入与门和非门电路若干。

实验内容及说明

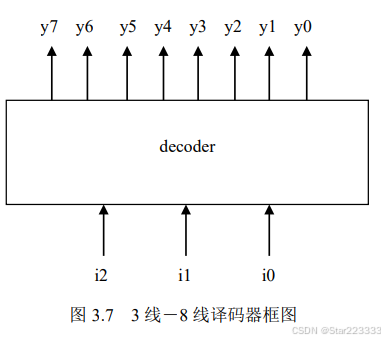

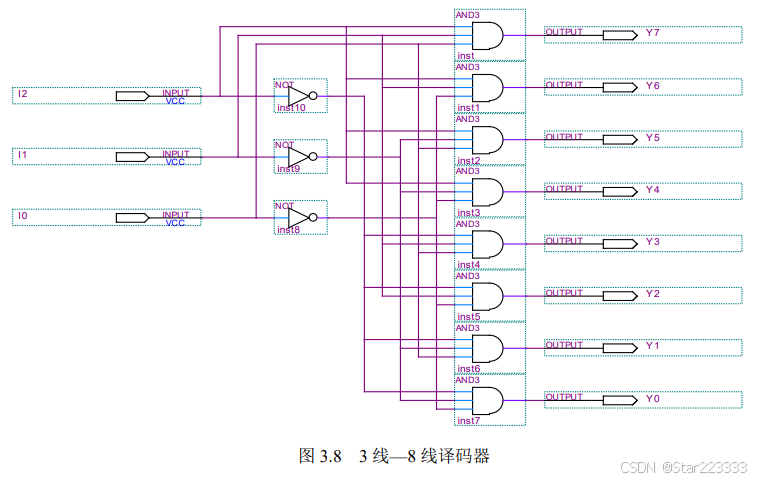

本实验要求完成一个 3 线-8 线译码器的设计。其中 i2-i0 为译码器输入端,y7-y0 为译码器输出 端。图 3.7 为三线―八线译码器的框图,图 8 给出了三线―八线译码器的原理图。

实验步骤

(1)原理图输入:根据图 3.8 电路,采用图形输入法完成实验电路的原理图输入。

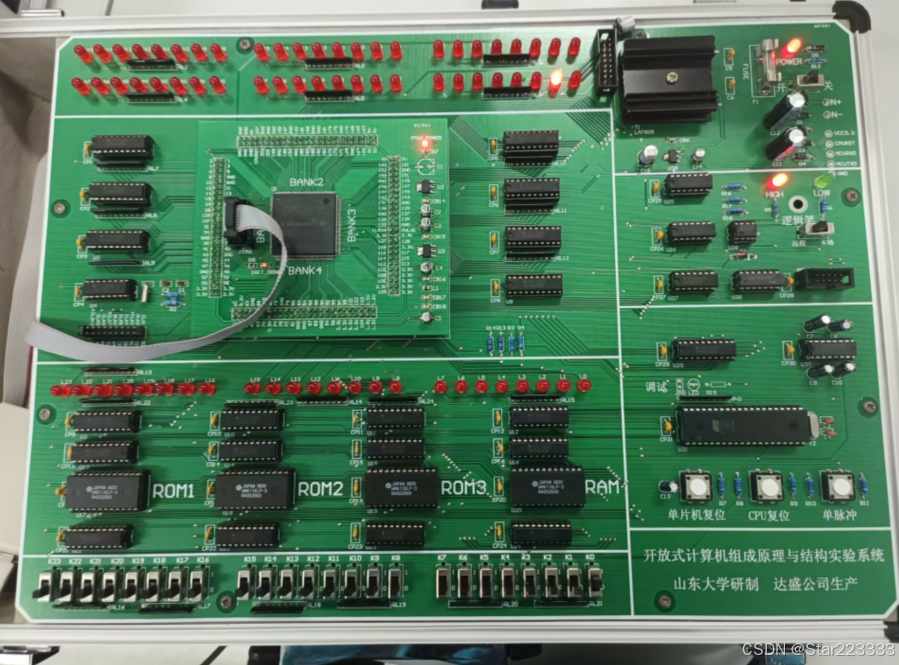

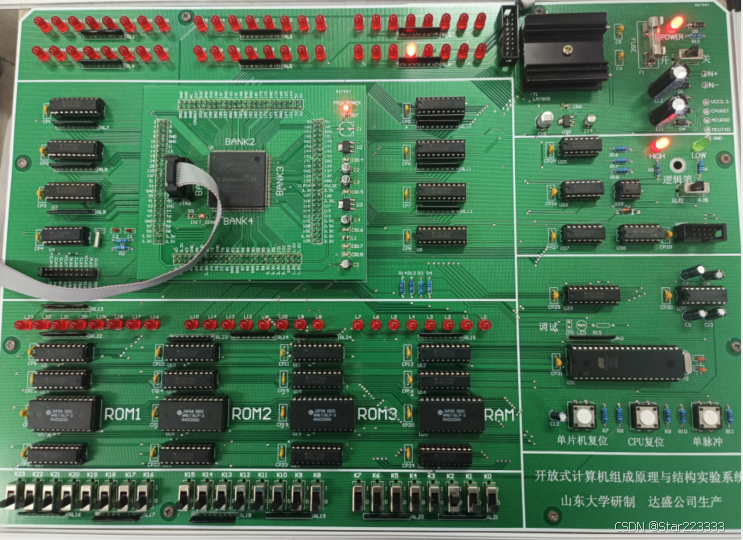

(2)管脚定义:根据图 3.1 硬件实验平台资源示意图和附录一 平台资源和 FPGA 引脚连接表完 成原理图中输入、输出管脚的定义。 将译码器的三个输入端分别定义在 K2-0 上。 将译码器的三个输出端分别定义在 LD7-0 上。I2对应PIN_81,I1对应PIN_80,I0对应PIN_77。Y0对应PIN_142,Y1对应PIN_143,Y2对应PIN_144,Y3对应PIN_145,Y4对应PIN_146,Y5对应PIN_147,Y6对应PIN_149,Y7对应PIN_150。I2-0定义在K2-0上,Y7-0定义在LD7-0上。

(3)原理图编译、适配和下载:在 QuartusⅡ环境中选择 EP2C8Q208C8 器件,进行原理图的 编译和适配,无误后完成下载。

(4)功能测试:改变 K2-0 的状态,译码器的输出则相应改变。

(5)生成元件符号。

实验结果

当输入全为0时,输出只有Y0为1,符合预期

当输入I0为1,其余为0,输出只有Y1为1,符合预期:

当输入I2为1,其余为0,输出Y4为1,符合预期:

当输入I2I1为1,其余为0,输出Y6为1,符合预期:

波形图为:

如能打赏,不胜感激[叩谢]。