系列目录

- 持续更新~

- 欢迎评论区留言指正

- 如果你是Obsidian用户,可以导入自己的笔记库中,效果最佳

- ⚠️如需转载,请标明出处!

第一章 计算机系统概述

1.1 计算机的发展(不考)

计算机系统= 硬件+软件

- 软件

- 软件的分类

- 系统软件——用来管理计算机系统

如:操作系统、数据库管理系统(DBMS) - 应用软件——按任务需要编制成的各种程序

- 系统软件——用来管理计算机系统

- 软件的发展

- 编程语言的发展

- 系统软件的发展

- 软件的分类

ENIAC——世界上第一台电子数字计算机(1946)

通过手动接线来控制计算

- 硬件

- 硬件的发展

- 第一代:电子管时代——高级计算语言:FORTRAN、操作系统雏形

- 第二代:晶体管时代

- 第三代:中小规模集成电路时代——分时操作系统

- 第四代:大规模、超大规模集成电路时代——“微处理器CPU”、微型计算机、PC

- 微处理器的发展

- 机器字长:计算机一次整数运算所能处理的二进制位数——8位、16位、32位、64位

- 8080——8位

- 8086——16位

- …Pentium——64位…

- 硬件发展的历史(1947-1969)

- 摩尔定律

- 硬件的发展

1.2 计算机硬件的基本组成

1.2.1 计算机硬件组成

- 计算机硬件的基本组成

- 五大部分(存储器分为内存储器和外存储器)

- I/O设备(+外存储器=外设)

- 输入设备

- 输出设备

- 主机

- 主存储器(内存储器):存放数据和程序

- CPU

- 运算器:算术运算、逻辑运算

- 控制器:指挥各部件、使程序运行

- I/O设备(+外存储器=外设)

- 五大部分(存储器分为内存储器和外存储器)

EDVAC——世界上第一台冯诺依曼结构的计算机

-

早期冯诺依曼机结构

- 首次提出“存储程序”概念

- 冯·诺伊曼机的特点:

- 以运算器为中心

-

现代计算机结构

- 以存储器为中心

- CPU=运算器+控制器

1.2.2 各个硬件的工作原理🌟

存储体:

MAR(存储地址寄存器,Memory Address Register):

MDR(存储数据寄存器,又称存储通用寄存器,Memory Data Register):

⚠️注意:现在的计算机通常也把MAR、MDR集成在CPU内

- 主存储器的基本组成

- 相关概念

- 存储单元:每个存储单元存放一串二进制代码(每一个地址对应一个存储单元)

- 存储字(word):存储单元中二进制代码的组合

- 存储字长:存储单元中二进制代码的位数

- 存储元:

- 主存储器的组成

- 存储体:数据在存储体内按地址存储

- MAR:MAR位数反应存储单元的个数

- MDR:MDR位数=存储字长

例如:

若MAR=4位->共有2^4个存储单元

若MDR=16位->每个存储单元可存放16bi,(此时)1个字(word)=16bit

- 运算器的基本组成(前三个必须具备)

- ACC(累加计数器):

- MQ(乘商寄存器):

- X(通用寄存器):

- ALU(算术逻辑单元):

- 控制器的基本组成

- CU(控制单元):

IR(指令寄存器):

PC(程序计数器):

- CU(控制单元):

- 工作过程

- 初始:指令、数据存入主存,PC指向第一条指令(此时PC=0)

- 从主存中取指令放入IP、PC自动加1、CU分析指令、CU指挥其他部件执行指令

- 相关概念

1.2.3 计算机系统的层次结构

编译、汇编、解释程序可统称为解释程序

- 计算机系统的层次结构

- 软件

- 虚拟机器 M4(高级语言机器):执行高级语言

- 虚拟机器 M3(汇编语言机器):执行汇编语言

- 虚拟机器 M2(操作系统机器):向上提供广义指令

- 硬件(计组主要讨论)

- 传统机器 M1(用机器语言的机器):执行机器语言指令

- 微程序机器 M0(微指令系统):执行微指令

- 软件

- 三个级别的语言

- 语言

- 高级语言

- 汇编语言

- 机器语言

- 程序

- 编译程序——

- 汇编程序——

- 解释程序——

- 语言

1.3 计算机的性能指标🌟🌟

总容量:存储单元个数x存储字长,单位bit(Byte)

例:MAR为32位,MDR为8位

总容量 = 2 32 × 8 b i t = 4 G B = 2^{32} \times 8 bit = 4GB =232×8bit=4GB

CPU主频——单位为Hz的含义——每秒钟振荡的次数(CPU时钟周期数)——时周数/s

执行一条指令的耗时 =CPI x CPU时钟周期

CPU执行时间(整个程序的耗时) = CPU总时钟周期数/主频 = (指令条数 x CPI)/主频

IPS =主频/平均CPI——指令数/s

其中CPI——时周数/指令,/表示“每”

🌟公式推导的独家方法:将上述的P当成/,也就是分号

IPS=I/S

CPI=C/I

主频=C/S——时钟周期数

- 存储器的性能指标

- 总容量:

- CPU的性能指标

- 相关概念

- CPU主频(时钟频率):CPU内数字脉冲信号振荡的频率,单位:Hz

- CPU时钟周期:(与CPU主频互为倒数,)单位:微秒us、纳秒ns

- CPI(Clock Per Instruction):执行一条指令所需的时钟周期数 ⚠️注:不同的指令CPI不同,相同的指令CPI也不一定相同,一般讨论平均CPI

- IPS(Instructions Per Second):每秒执行多少条指令

- FLOPS(Floating-point Operations Per Second):每秒执行多少次浮点运算,KFLOPS、MFLOPS、GFLOPS、TFLOPS(此处KMGT为计网量纲)

- 相关概念

- 系统整体的性能指标

- 数据通路带宽:数据总线一次所能并行传送信息的位数(各硬件通过数据总线传输数据)

- 吞吐量:指系统在单位时间内处理请求的数量

- 响应时间:通常包括

- CPU时间——运行一个程序花费时间

- 等待时间——磁盘访问、存储器访问、I/O操作、操作系统开销等

- 基准程序(动态测试):也就是常见的“跑分软件”,测量计算机处理速度

第二章 数据的表示和运算

2.1 数据

2.1.1 进位计数制

二进制——B——Binary

十六进制——H——Hexadecimal或者0x,如0x1652

十进制——D——Decimalism

例: (1682)16 = 1682H

⚠️:有的十进制数无法用二进制精确表示,如:0.3

0.3D=0.01001…B

真值->机器数

+15->0 1111

-8->1 1000

- 各种进制

- 罗马数字

- 十进制

- r进制

- 二进制(使用原因)

- 可使用两个稳定状态的物理器件表示

- 0,1正好对应逻辑值真、假,方便实现逻辑运算

- 可很方便地使用逻辑门电路(一种处理二进制的元器件)实现算术运算

- 八进制

- 十六进制

- 二进制(使用原因)

- 🌟其他进制转换成十进制

- 🌟二、八、十六进制之间的相互转换(注意补位)

- 二进制->八进制:3位一组(注意补位)

- 二进制->十六进制:4位一组(注意补位)

- 八进制->二进制:1位对应用3位表示

- 十六进制->二进制:1位对应用4位表示

- 🌟十进制转换成其他进制

- 十进制->r进制

- 整数部分——除基取余法(转换成什么进制——基就取r,也就是除数取r),取数应从下往上(最下面的数是最高位)

- 小数部分——乘基取整法,取数应从上往下(最上面的数为小数部分的最高位)

- 🌟十进制->二进制->r进制

- 拼凑法——先用拼凑法将十进制数转换成二进制再转换成对应的r进制

- 十进制->r进制

- 真值和机器数(有个了解即可)

- 真值:实际的带正负号的数值

- 机器数:把正负号数字化的数(如:0表示+,1表示-)

2.1.2 BCD码(Binary-Coded Decimal)(不考)

- 计算方法:相加所得结果大于等于10,对应二进制就需要加6进行修正(+0110)

- 常见的BCD码

- 8421码

- 余3码(无权码——每一位的权制并不固定)

- 2421码

2.1.3-2.1.4 符号整数的表示和运算

- 无符号整数

- 加法运算——从最低位开始,按位相加,向更高位进位

- 减法运算(补码)——被减数不变,减数全部位按位取反、末位+1,减法变加法

- 带符号整数(整数,又称定点整数)

short型(短整型,2B)、int型(整型,4B)

计算机内部,所有带符号整数的加减法都要先转换成对应的补码- 原码

- 0正1负、机器字长n+1位,表示范围±(2^n-1),真值0有两种形式[±0]原

- 反码

- 正数——原码、反码、补码相同

- 负数

- 原码与反码互相转换:符号位不变,数值位取反,[x]原<->[x]反

- 反码转换成补码:末位+1,[x]反->[x]补

- 补码

- 原码直接转换成补码(相互转换):自右向左找到第一个1,将其左边的所有数值位按位取反

- [B]补与[-B]补相互转换:全部位按位取反、末位+1

- 补码的减法运算——被减数不变,减数全部位按位取反、末位+1,减法变加法(与无符号整数相同,用同一套电路即可处理所有的加减法,省钱)

- 原码

2.1.5 原反码的特性对比

🌟带符号整数的补码,合法表示范围为-2^n ≤ x ≤ 2^n-1,比原码多一个负数

且只有一种方法表示真值0,[0]补=0,000…0000(真值0只有一种补码)

2.1.6 移码

移码:补码的基础上将符号位取反

⚠️:移码只能用于表示整数

四码之间的转换(练习)

2.1.7 定点小数

- 定点数

- 定点整数——带符号整数

- 定点小数

- 定点小数

- 原码:各个bit的位权不同—— 2 − 1 、 2 − 2 . . . 2^{-1}、2^{-2}... 2−1、2−2...

- 原码/反/补码——与定点整数相同

- 加/减运算——先转换为补码(符号位参与运算)——其余与定点整数相同

🌟2.2 运算方法和运算电路

2.2.0 奇偶校验码(大纲已删)

- 校验原理

- 奇偶校验

- 奇校验:整个校验码(有效信息位和校验位)中的1的个数为奇数

- 偶校验:整个校验码中的1的个数为偶数

- 检测不出偶数个位发生错误

- 硬件实现

- ⊕:异或(模2加)

- 0⊕0 = 0

- 0⊕1 = 1

- 1⊕0 = 1

- 1⊕1 = 0

- 偶校验:各信息进行异或(模2加)运算,得到的结果即为偶校验位,如01001101——1⊕0⊕0⊕1⊕1⊕0⊕1=0(偶校验位为0)

- ⊕:异或(模2加)

2.2.1 电路的基本原理、加法器设计

- 算术逻辑单元(ALU)

- 作用、大致原理

- 功能

- 算术运算:四则运算

- 逻辑运算:与、或、非、异或等

- 辅助功能:移位、求补等

- 功能

- 电路基础知识

-

最基本的逻辑运算(表达式——真值表——门电路)

门电路的输入输出信号本质上就是一些高低电平(5V/1V)

非门的门电路图示中有个小圈圈

优先级:与>或- 与——Y=A·B——类比C语言中“&&”——“与门”——天然逻辑“屏蔽“

- 或——Y=A+B——“||”

- 非——Ā——“!”

-

复合逻辑

反演律(德摩根律):

A + B ‾ = A ‾ ⋅ B ‾ A ⋅ B ‾ = A ‾ + B ‾ \overline{A+B}= \overline{A} · \overline{B} \\ \overline{A · B} = \overline{A} + \overline{B} A+B=A⋅BA⋅B=A+B- 与非

- 或非

- 异或⊕

-

- 加法器的实现

- 作用、大致原理

2.2.2 并行进位加法器(佛系一点)

2.2.3 补码加减运算器(新考点)

- 加法器原理

2.2.4 加减运算的补充

2.2.4.1加减运算和溢出判断

- 加减运算

- 原码的加减运算

- 补码的加减运算

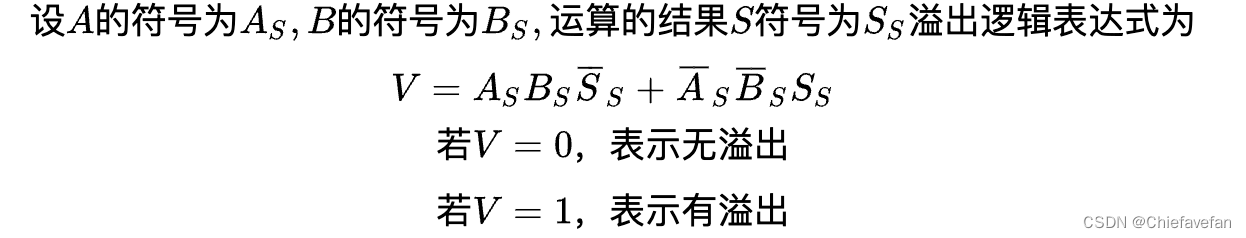

- 溢出判断

-

采用一位符号位

-

采用一位符号位,根据数据位进位情况判断溢出——插入LaTex

-

🌟采用双符号位

实际存储时只存储1个符号位,运算时会复制一个符号位(不会增加存储空间)

-

2.2.4.2 标志位的生成(对加法器2.2.3的补充, 新考点)

- 标志位的生成

- OF(Overflow Flag)溢出标志(仅对有符号数加减法有意义)

- SF(Sign Flag)符号标志(仅对有符号数加减法有意义)

- ZF(Zero Flag)零标志

- CF(Carry Flag)进位/借位标志(仅对无符号数加减法有意义)

2.2.5 定点数的移位运算

- 🌟算数移位

- 原码(定点小数同理)——符号位保持不变,仅对数值进行移位

- 右移:高位补0,低位舍弃…相当于÷2,舍弃位≠0——丢失精度

- 左移:低位补0,高位舍弃…相当于x2,舍弃位≠0——严重误差

- 反码(负数反码的移位运算)

- 右移:高位补1,低位舍弃

- 左移:低位补1,高位舍弃

- 🌟补码

规律:负数补码中,最右边的1及其右边同原码;左边同反码- 右移(同反码):高位补1,低位舍弃

- 左移(同原码):低位补0,高位舍弃

- 总结:左移相当于x2;右移相当于÷2——左乘右除

负数补码移位规律——右反高1,左原低0 - 应用举例:-20x7->-20x( 2 0 + 2 1 + 2 2 2^0+2^1+2^2 20+21+22),相当于-20依次加上-20不左移、左移1位、左移2位

- 原码(定点小数同理)——符号位保持不变,仅对数值进行移位

- 逻辑移位(看作“无符号数”的算数移位——高/低补0)

- 逻辑右移:高位补0,低位舍弃

- 逻辑左移:低位补0,高位舍弃

- 应用举例:RGB=R+G+B——Red+Green+Blue——红绿蓝

R=用3B存储无符号数,逻辑左移16位

G=用3B存储无符号数,逻辑左移8位

B=用3B存储无符号数

相加得3B的RGB值

- 循环移位

- 循环左/右移(字面意思)

- 带进位(CF)为的循环左/右移:同理

- 不带进位位…

- 应用举例:汉字“啊”——占2B位置;

大端存储:先存放高字节,再存放低字节

小端存储:先存放低字节,再存放高字节

可以通过循环左移8位,实现大/小端存储的调换

- 循环左/右移(字面意思)

2.2.6 定点数的乘法运算

2.2.6.1 原码的乘法运算

- 乘法运算的实现思想

通过“移位”实现—— × 2 − 5 相当于右移 5 位 , × 2 5 相当于左移 5 位——左乘右除 \times2^{-5}相当于右移5位,\times2^5相当于左移5位——左乘右除 ×2−5相当于右移5位,×25相当于左移5位——左乘右除- 运算器

- ACC——(存储)乘积高位

- MQ——乘数、乘积低位

- X——被乘数(被乘数绝对值的原码)

- 运算器

- (定点数)原码的一位乘法(参与运算的当前位只有1位)

- 符号位单独处理:符号位 X S ⊕ Y S X_S⊕Y_S XS⊕YS

- 数值位:取绝对值进行乘法计算

- 实现方法:先加法再移位(逻辑右移,高位补0),重复n次(数值位为n位)

- 🌟运算过程(进行乘法之前,ACC置0):画运算器图,手动模拟!

当前位=1,(ACC)-(被乘数)->ACC(在ALU中完成),即 ( A C C ) + [ ∣ x ∣ ] 原 (ACC)+[|x|]_原 (ACC)+[∣x∣]原

当前位=0,ACC加上0

每次加法操作后,ACC、MQ统一逻辑右移1位,(ACC)高位补0,执行n次

最后修改符号位—— X S ⊕ Y S = 1 / 0 X_S⊕Y_S=1/0 XS⊕YS=1/0

2.2.6.2 补码的乘法运算

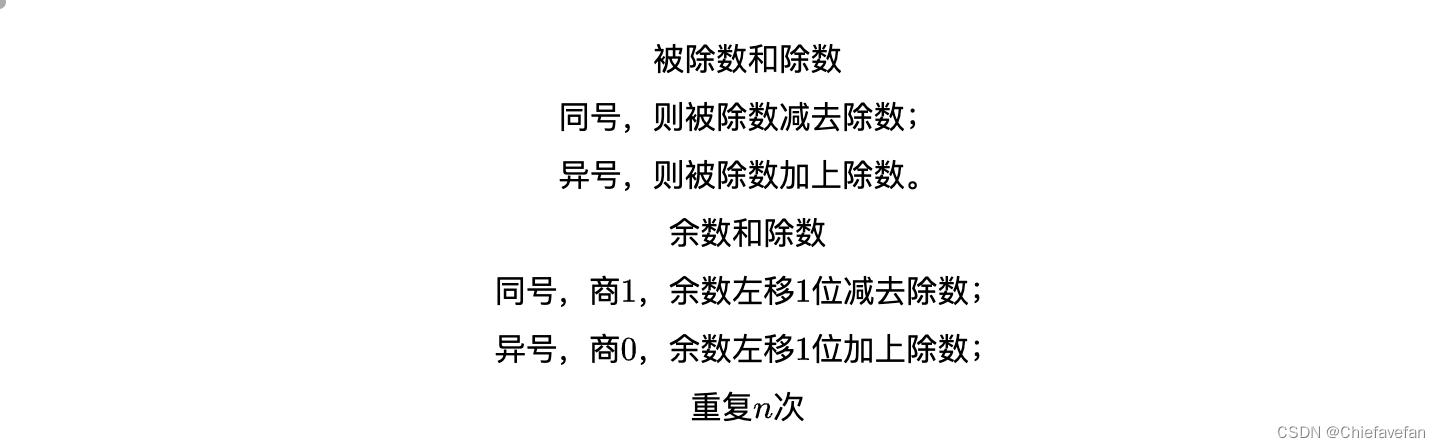

2.2.7 定点数的除法运算

2.2.7.1 原码的除法运算

- 除法运算的实现思想

- 运算器

- ACC(Accumulator)——被除数、余数

- MQ(Multiple-Quotient register)——商

- X——除数

- 运算器

- 🌟原码除法

- 恢复余数法

- 符号位单独处理:符号位 X S ⊕ Y S X_S⊕Y_S XS⊕YS

- 数值位:取绝对值进行除法计算

- 实现方法:上商0/1,得到余数,余数末尾补0

- 🌟运算过程:画运算器图,手动模拟!

默认上商1,如果出错再改上商0,并“恢复余数”(相减结果为负数, 上商0)

求余数:

(ACC)-(除数)->ACC,即

( A C C ) + [ − ∣ y ∣ ] 补 − > A C C (ACC)+[-|y|]_补->ACC (ACC)+[−∣y∣]补−>ACC(,若ACC为负数,则“恢复余数”)

恢复余数:

(ACC)+(除数)->ACC,即

( A C C ) + [ ∣ y ∣ ] 补 − > A C C (ACC)+[|y|]_补->ACC (ACC)+[∣y∣]补−>ACC(,改上商0)

每次减法操作后,ACC、MQ统一逻辑左移1位,(MQ)低位补0,执行n次

==注:==若最后一步商余数为负,还需要再恢复一次余数并商0

若为定点小数的除法运算,则小数点隐含位置应在符号位后

真实余数还需要在ACC中数的基础上在 × 2 − n \times2^{-n} ×2−n

如, 余数 = 0.0111 × 2 − n 余数=0.0111\times2^{-n} 余数=0.0111×2−n

最后修改符号位—— X S ⊕ Y S = 1 / 0 X_S⊕Y_S=1/0 XS⊕YS=1/0

- 加减交替法(不恢复余数法)

- 恢复余数法

2.2.7.2 补码的除法运算

- 🌟补码除法

- (补码)加减交替法(不恢复余数)

- 符号位参与运算(被除/余/除数均采用双符号位,其中01表正,10表负)

- 实现方法:

- (补码)加减交替法(不恢复余数)

2.2.8 C语言类型转换

2.2.9 数据的存储和排列

现代计算机通常是按字节编址,即每个字节对应1个地址——通常也支持按字、按半字、按字节寻址

假设存储字长(机器字长)为32位,则1个字=32bit,半字=16bit。

每次访存只能读/写1个字

- 大小端模式

最高有效字节(MSB)、最低有效字节(LSB)- 大端方式——内存地址从低到高——便于人类阅读——先读入最高有效字节

- 小端方式——便于机器处理——先读入最低有效字节(最应先被处理的字节)

- 边界对齐

- 边界对齐方式——空间换时间

- 边界不对齐方式

🌟2.3 浮点数的表示和运算

2.3.1 浮点数的表示

- 浮点数的作用和基本原理

- 浮点数规格化

- 浮点数的表示范围(大纲已删)

2.3.2 IEEE 754 标准

两个重要的例子:(Goodnotes手算)

- 将==-0.75D==转换成IEEE 754 的单精度浮点数格式(float)表示

- IEEE 754 的单精度浮点数 C0 A0 00 00 H的值(浮点数真值)为多少

2.3. 3 浮点数的(加减)运算

- 🌟(浮点数的)加减运算

- 运算步骤

- (做题时一般要先进行)真值到机器数的转换

- 对阶

- 尾数加减(尾数求和)

- 规格化

- 舍入

- "0"舍"1"入法

- 恒置"1"法

- 截断法(恒舍法)

- 溢出判断

- 阶码上溢——抛出异常(中断)——说明此时发生的是正/负上溢

- 阶码下溢——按机器0处理——超出阶码负数所能表示的最小值

- 运算步骤

- (C语言)强制类型转换(浮点数与定点数之间)

- 无损

- char->int->long->double

- float->double

范围、精度从小到大,转换过程没有损失(默认32位机器)

- 🌟(常考)有损——32位(机器)

- int->float(int向float转换):可能会损失精度

- float->int:可能溢出(float表示范围超出)及损失精度

int:表示整数,范围 − 2 31 ∼ 2 31 − 1 -2^{31} \sim 2^{31}-1 −231∼231−1,有效数字32位(int型变量表示一个定点的整数,1个符号位+31个有效的数值位)

float:表示整数及小数,范围 ± [ 2 − 126 ∼ 2 127 × ( 2 − 2 − 23 ) ] ±[2^{-126}\sim2^{127}\times(2-2^{-23})] ±[2−126∼2127×(2−2−23)],有效数字23+1=24位(float型变量,1个符号位+8个阶码+23个尾数(23位尾数之前实际还有一个隐含的1——实际有效数值应为24位))

- 无损

第三章 存储系统

3.1 存储系统的概念

- 🌟层次结构

- 高速缓存(Cache)——可直接被CPU读写

- 主存储器(主存、内存)——可直接被CPU读写

- 辅助存储器(辅存、外存)

- 分类

- 按层次结构(同上)

- 按存储介质

- 半导体存储器

- 磁表面存储器

- 光存储器

- 🌟按存取方式

- 按地址访问的存储器

- RAM(Random Access Memory)随机存取存储器——如内存

- SAM(Sequential Access Memory)顺序存取存储器——如磁带(Sequential 按顺序的)

- DAM(Direct Access Memory)直接存取存储器——如磁盘

- 按内容访问的存储器

- CAM(Content Access Momory)相联存储器——如快表

- 按地址访问的存储器

- 按信息可更改性

- RWM(Read/Write Memory)读/写存储器——即可读,也可写

- 如:磁盘、内存、Cache

- ROM(Read-Only-Memory)只读存储器

- 如:实体专辑CD-ROM,实体蓝光光碟,BIOS通常写在ROM中——集成在主板上

- RWM(Read/Write Memory)读/写存储器——即可读,也可写

- 按断电后信息是否消失

- 易失性存储器——如主存(内存)、Cache

- 非易失性存储器——如磁盘、光盘

- 按信息读出后,原信息是否被破坏

- 破坏性读出——如DRAM芯片——读出数据后要进行重写

- 非破坏性读出——如SRAM芯片、磁盘、光盘

- 存储器性能指标

- 存储容量=存储字数(MAR位数,如 2 32 2^{32} 232)x存储字长(MDR位数,如8位)

- 单位成本(每位价格)=总成本/总容量

- 🌟数据传输率(主存带宽Bm)=数据的宽度/存储周期

- 🌟存取周期™=存取时间(Ta)+恢复时间

3.2 主存储器

3.2.1 主存储器的基本组成

- 基本元件(DRAM)

- MOS管,一种通电开关——半导体元器件——低电平绝缘体,高电平导体

- (栅极)电容,存储电荷(即存储二进制0/1)——两端电压差(一端接地)——电荷移动

- 存储芯片的结构

- 译码驱动电路

- 译码器将地址信号转化为字选通线的高低电平

- 存储矩阵(存储体)

- 由多个存储单元组成,存储单元又有多个存储元组成

- 读写电路

- 每次读/写一个(存储)字——4B

- 地址线、数据线、片选线(

C

S

‾

/

C

E

‾

\overline {CS}/\overline {CE}

CS/CE)、读写控制线(一根/两根读写线

W

E

‾

低电平写

/

高电平读;

W

E

‾

允许写,

O

E

‾

允许读

\overline {WE}低电平写/高电平读;\overline {WE}允许写,\overline {OE}允许读

WE低电平写/高电平读;WE允许写,OE允许读)

CS——Chip Select(片选信号)、CE——Chip Enable(片使能…)

WE——Write Enable(写使能…)、OE——Output Enable(输出使能…)

注:上划线表示该信号低电平有效

- 译码驱动电路

- 寻址

- 现代计算机通常按字节编址(每个字节),即每个字节对应一个地址

- (也可)按字节寻址、按字寻址、按半字寻址、按双字寻址

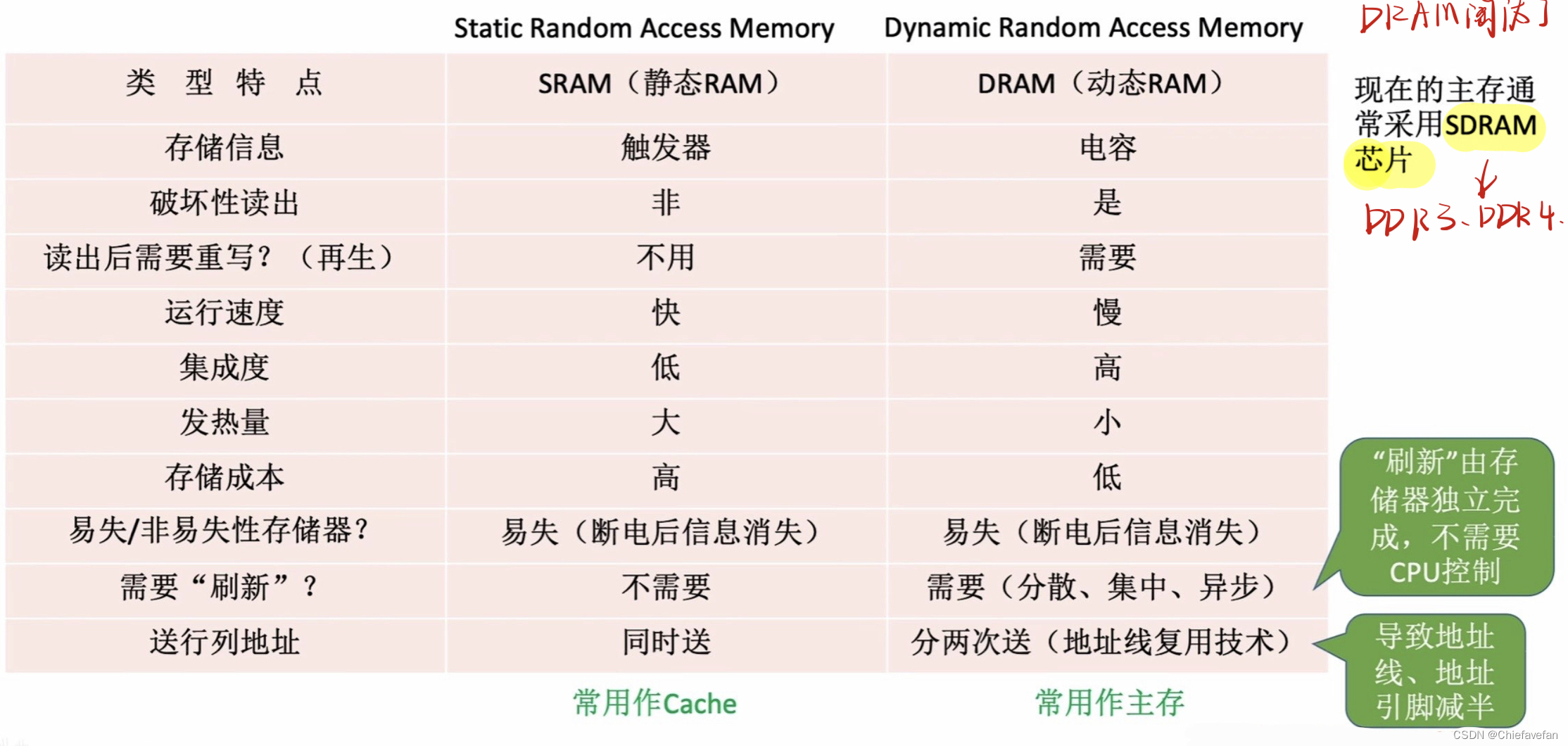

3.2.2 DRAM和SRAM(RAM)

Dynamic Random Access Memory,即动态RAM

Static Random Access Memory,即静态RAM

DRAM用于主存、SRAM用于Cache

🌟高频考点:DRAM、SRAM的区别

- 🌟存储元件不同导致的特性差异(核心区别:存储元不同)

- DRAM——栅极电容(1个MOS管)

- 电容放电后信息被破坏(破坏性读出),读出后应有重写操作,也成“再生”——读写速度更慢

- 一条数据线

- 读出1(电容内存储了电荷):MOS管接通,电容放电,数据线上产生电流

- 读出0(电容内未存储电荷):MOS管接通,数据线上无电流

- SRAM——双稳态触发器(6个MOS管)

- 读出数据,触发器状态保持稳定(非破坏性读出),无需重写——读写速度更快

- 两条数据线

- BL——读出0时,BL为低电平

- BLX——读出1时,BLX为低电平

- DRAM——栅极电容(1个MOS管)

- DRAM的刷新

电荷内的电荷只能维持2ms。即使不断电,2ms后信息也会消失。2ms内必须刷新一次(给电荷充电)- 刷新有关问题——行缓冲

- 刷新周期:一般为2ms

- 行缓冲:以行为单位,每次刷新一行存储单元——行缓冲长度

- 使用行列地址:减少选通线的数量

- 刷新方式:有硬件支持,读出一行的信息后重新写入,占用1个读/写周期(即只占用1个存储周期)

- 何时刷新:假设DRAM内部结构排列128x128的形式,读/写周期(存储周期)0.5us,2ms共4000个周期

- DRAM的刷新分类

![[IMG_336299E90414-1.jpeg]]- 分散刷新——优点:没有“死时间”

- 集中刷新

- ✅异步刷新

- 刷新有关问题——行缓冲

- 🌟🌟DRAM的地址线复用技术——地址线减半(一看到DRAM)

- 行、列地址分两次送(先接收行地址,再接收列地址),可使地址线减半,芯片引脚更少

- 🌟DRAM、SRAM的区别与联系

3.2.3 ROM

RAM芯片——易失性——DRAM用于主存、SRAM用于Cache

ROM芯片——非易失性——磁盘、固态硬盘SSD、辅存

==注:==很多ROM也可以写,也具有“随机存取”的特性——访问速度不受地址影响

- 常见的ROM

- MROM(Mask)——掩模式只读存储器

- PROM(Programmable …)——(一次)可编程只读存储器

- EPROM(Erasable …)——可擦除可编程只读存储器——

根据擦除方式不同- UVEPROM——Ultraviolet rays Erasable …——紫外线擦除

- EEPROM——Electrically Erasable…——点擦除

- 闪存(Flash Memory,闪速存储器)——用于U盘、CD卡

- 注:闪存一般写速度比读速度慢——写入前要擦除

- SSD(Solid State Drives,固态硬盘)

组成部分- 控制单元

- 存储单元(Flash芯片)

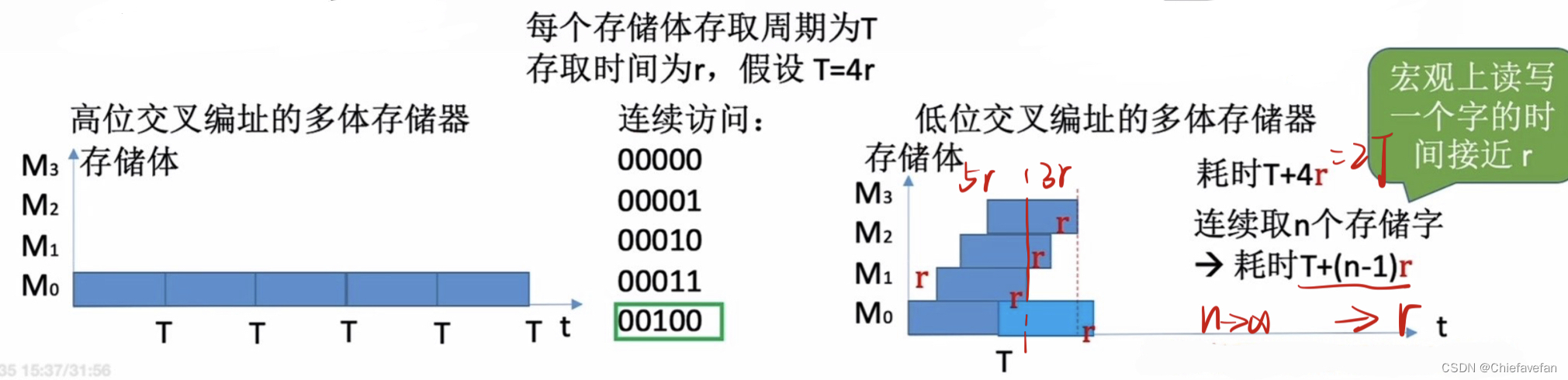

3.2.4 双端口RAM(大纲已删)和多模块存储器🌟

存取周期:可以连续读/写的最短时间间隔

存取周期T=存取时间r+恢复时间

提升主存速度

-

双端口RAM(408不考——了解即可)

- 特点:

- 支持两个CPU同时访问RAM

- 可同时读,但不可同时写——对比联系操系“读者-写者”问题

- 发生冲突——“BUSY”信号——另一个CPU的访问端口暂时关闭

- 作用:优化多核CPU访问一根内存条的速度

- 特点:

-

多模块存储器

- 单体多字存储器——🚫指令和数据在主存内必须是连续存放的

- 每次并行读出m个连续的字

- 总线宽度也要拓展为m个字

- 多(m)体并行存储器——既能并行工作,又能交叉工作

给定地址x,确定属于第几个存储体

法一:根据末尾的二进制体号

法二:模块序号=十进制地址x%交叉模块数m-

高位交叉编址

不满足局部性原理,无法使用“流水线”方式- 理论上——多个存储体可被并行访问

- 实际上——大多数情况下会连续访问——实际效果相当于单纯的扩容

-

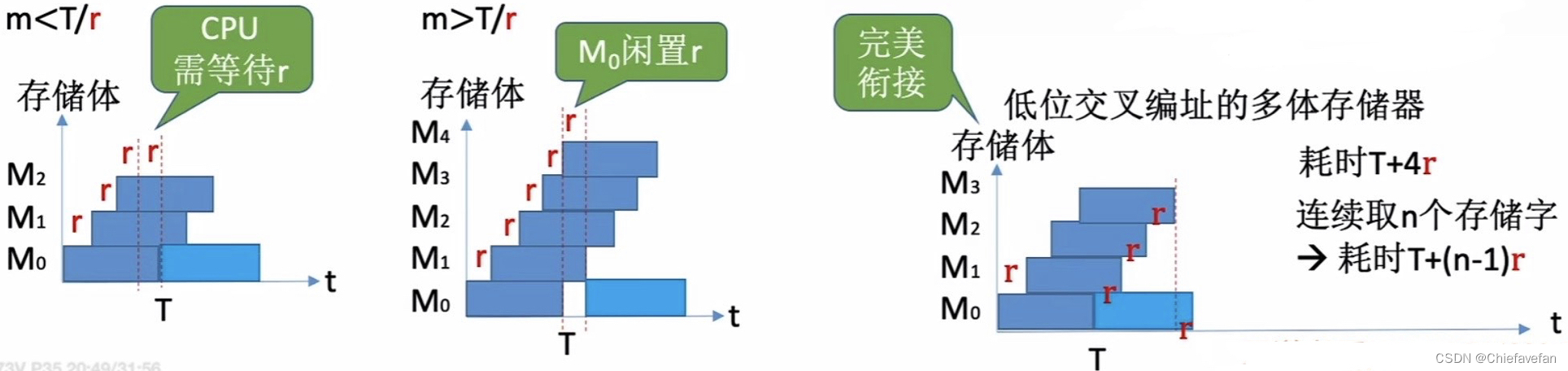

🌟低位交叉编址( m = T r m=\frac {T}{r} m=rT完美)

==其中:==m为存储体的个数(m体交叉存储器),T为存取周期,r为存取时间

408中,默认交叉编织都为低位交叉编织

每个芯片的片选信号由最低位地址确定;高位为片内地址

- 当存储模块数 m ≥ T r m≥\frac {T}{r} m≥rT时,可使流水线(并行存取)不间断

- 每个存储周期内可读写地址连续的m个字

- 低位交叉编织器采用==”流水线“方式并行存取==——宏观上并行,微观上串行——连续访问m个模块

- 宏观上——每个存取周期内所有的模块被并行访问

- 微观上——m个模块被串行连续访问

-

- 单体多字存储器——🚫指令和数据在主存内必须是连续存放的

3.3 主存储器与CPU的连接

-

单块存储芯片与CPU的连接

MAR、MDR一般集成在CPU中- 地址总线(MAR=存储单元的个数 2 x 2^x 2x)

- 数据总线(宽度=存储字长=MDR位数)

- 控制总线——一般仅包括2条

- 读控制线

- 写控制线

- 片选线

-

多块存储芯片与CPU的连接

- 位扩展——增加主存的存储字长/提升CPU的寻址能力

- 字扩展——增加主存的存储字数

- 线选法——电路简单——地址空间不连续

- 以 8 K × 8 位为例, A 14 A 13 只能为 01 或 10 以8K\times8位为例,A_{14}A_{13}只能为01或10 以8K×8位为例,A14A13只能为01或10

- n条线->n个选片信号

- 若直接同时将片信号置为高电平,总线会冲突

- (译码器)片选法——电路复杂——地址空间可连续

- 引入非门:——|> ∘ \circ ∘——

- n条线-> 2 n 2^n 2n个选片信号

- 常见的有:1-2译码器、2-4译码器、3-8译码器

- 地址总线的编号可逆

- 线选法——电路简单——地址空间不连续

- 字位(同时)扩展

- 选择存储器芯片

- 与CPU进行连接

-

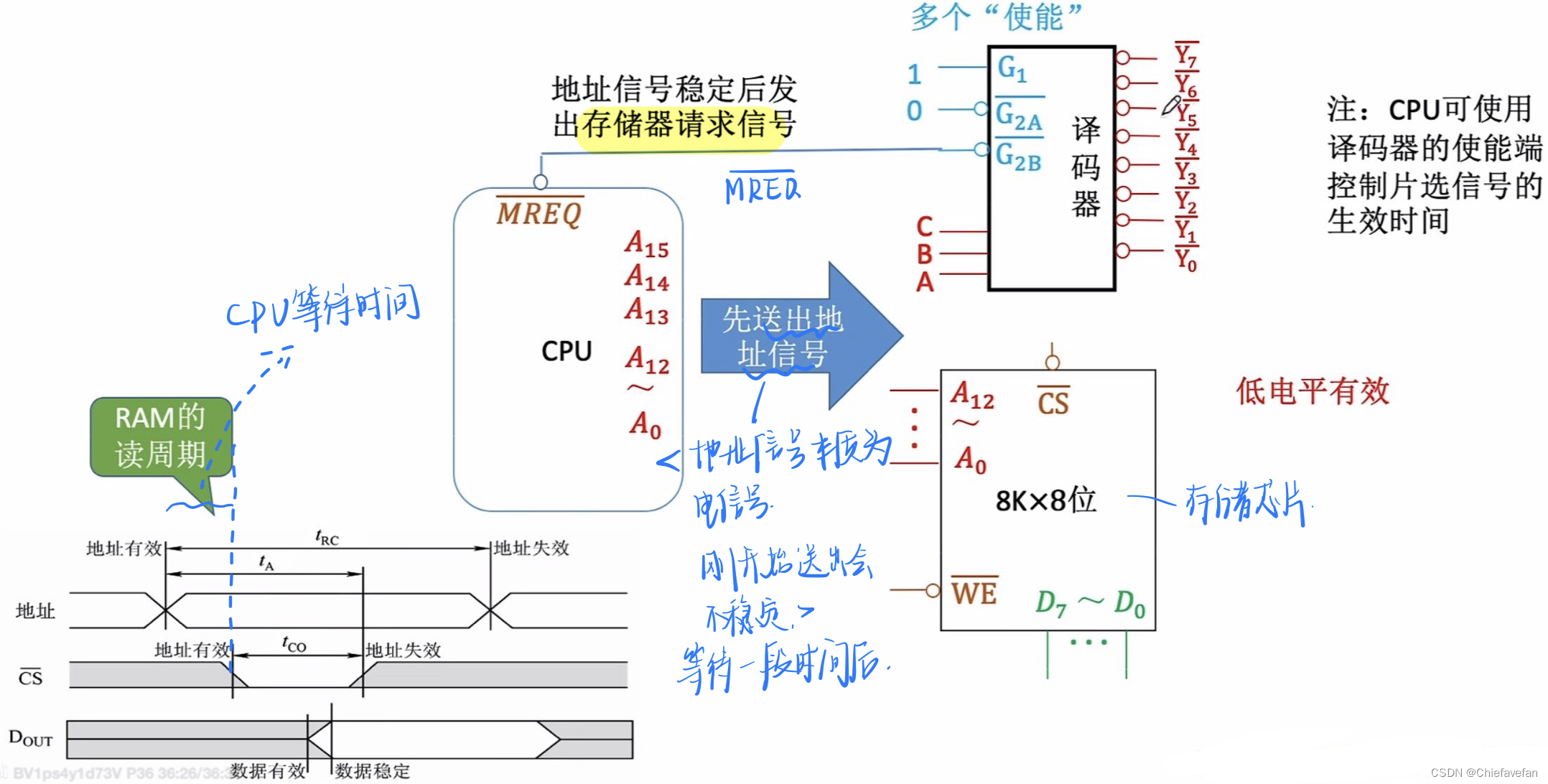

🌟译码器

- EN——Enable——使能信号——类似于CS(片选信号)

- 型号74ls138——多个使能信号—— G 1 , G 2 A ‾ , G 2 B ‾ G_1, \overline {G_{2A}}, \overline {G_{2B}} G1,G2A,G2B——1 0 0B表示运行

- CPU可使用译码器的使能端EN控制片选信号CS的生效时间

- CPU—— M R E Q ‾ \overline {MREQ} MREQ——存储器请求信号

- 使能信号的作用:保证存储芯片接收到的地址信号的稳定

- 地址信号本质为电信号——刚发送时CPU不稳定——需要等待一定时间后——地址信号稳定后发出存储器请求信号 M R E Q ‾ \overline {MREQ} MREQ

3.4 外部存储器

3.4.1 磁盘存储器

- 外存储器——又称辅助存储器——主要部分为磁表面存储器

- 特点

- 可同时作为I/O设备——读/写数据

- 磁表面存储器

- 读写操作均以1bit为单位

- 读写操作是串行的(若主机传输的是并行数据需要转换)

- 特点

- 磁盘原理

- 磁盘设备的组成

- 存储区域:磁头(Heads)、柱面(Cylinders)、扇区(Sectors)

- 磁盘存储器(磁盘驱动器+磁盘控制器)

- 磁盘驱动器

- 核心部件是磁头组件和盘片组件

- 温彻斯特盘是一种可移动头固定盘片的硬盘存储器

- 磁盘控制器

- 硬盘存储器和主机的接口

- 主流标准有IDE(本质ATA)、SCSI、✅SATA(SerialATA,串行ATA)

- ATA——Advanced Technology Attachment——高技术配置

- 磁盘驱动器

- 🌟性能指标

- 磁盘容量:格式化与非格式化—— 非格式化>格式化

- 记录密度

- 道密度:沿半径方向,单位长度上的磁道数

- 位密度:磁道单位长度上能记录的二进制代码位数

- 最外侧扇区与最内侧扇区均记录nbit信息

- 越内侧的磁道位密度越大

- 面密度:位密度X道密度

- 🌟平均存取时间:寻道时间+旋转延迟时间+传输时间(+磁盘控制器延迟时间)

- 寻道时间——磁头移动到目的磁道

- 旋转延迟时间——磁头定位到所在扇区(若题目没有明确表明,则取数学期望E=磁盘转半圈的时间)

- 传输时间——传输数据所花费的时间

- 磁盘控制器延迟时间

- 数据传输率:磁盘存储器在单位时间内向主机传送数据的字节数

- 假设磁盘转数为 r ( 转 / 秒 ) ,每条磁道容量为 N 个字节, 则数据传输速率 ( 理论峰值 ) 为 D r = r N 假设磁盘转数为r(转/秒),每条磁道容量为N个字节,\\则数据传输速率(理论峰值)为D_r=rN 假设磁盘转数为r(转/秒),每条磁道容量为N个字节,则数据传输速率(理论峰值)为Dr=rN

- 🌟磁盘地址:驱动器号|柱面(磁道)号|盘面号|扇区号

- 磁盘设备的组成

- 🌟磁盘阵列RAID

Redundant Array of Inexpensive Disks,廉价冗余磁盘阵列- 思想:利用磁盘廉价的特点提高存储性能、可靠性和安全性

- RAID0:条带化,提高存取速度,没有容错能力

- 逻辑上相邻的两个扇区在物理上存到两个磁盘,类比“低位交叉编址的多体存储器”

- RAID1:镜像磁盘互为备份

- 存两份数据

- RAID2:采用纠错的海明码的磁盘阵列

- 4bit信息位+3bit海明校验位

- 可纠正一位错,发现两位错

- RAID3~5:通过数据校验提高容错能力

3.4.2 固态硬盘(SSD)🌟新考点

- 原理

- 基于闪存技术——Flash Memory,属于电可擦ROM,即EEPROM

- 组成

- 闪存翻译层——负责翻译逻辑块号,找到对应的页(page)

- 存储介质:多个闪存芯片(Flash Chip)——每个芯片包含多个块(block)——每个块包含多个页(page)

- 🌟读写性能特性

区别:磁盘(存储器) 读写以块为单位——对应SSD的一个页- 以页(page)为单位读/写——相当于磁盘的“扇区”

- 以块(block)为单位“擦除”——相当于磁盘的“磁道”

- 擦干净的块,其中每一页都可以写一次,读无数次

- 支持随机访问(访问速度不受地址的影响)

- 系统给定一个逻辑地址,闪存翻译层可通过电路迅速定位到对应的物理地址

- 读快、写慢(先擦除再写)

- 要写的页如果有数据,则不能写入,需要将块内其他页全部复制到一个新的(擦除过的)块中,再写入新的页

- 与机械硬盘相比的特点

- SSD读写速度快,随机访问性能高,用电路控制访问位置;机械硬盘通过移动磁臂旋转磁盘控制访问位置,有寻道时间和旋转延迟

- SSD安静无噪音、耐摔抗震、能耗低、造价更贵

- 🌟SSD的一个块被擦除次数过多(重复写同一个块)可能会坏掉,而机械硬盘的扇区不会因为写的次数太多而坏掉

- 🌟磨损均衡技术

思想:将“擦除”平均分布在各个块上,以提升使用寿命- 动态磨损均衡

- 静态磨损均衡

3.5 高速缓冲存储器Cache🌟🌟🌟

3.5.1 Cache的基本概念和原理

- 工作原理

- 将某些主存块复制到Cache中,缓和CPU与主存之间的速度矛盾

- 局部性原理

- 时间局部性

- 现在访问的地址,不久之后也很可能被再次访问

- 空间局部性

- 现在访问的地址,其附近的地址也很可能即将被访问

- 时间局部性

- 性能分析

- Cache命中率H、缺失率M=1-H

- 两种方式

设 t c 为访问一次 C a c h e 所需时间, t m 为访问一次主存所需时间 设t_c为访问一次Cache所需时间,t_m为访问一次主存所需时间 设tc为访问一次Cache所需时间,tm为访问一次主存所需时间- 先访问Cache,发现未命中再访问主存

- Cache-主存系统的平均访问时间为 t = H t c + ( 1 − H ) ( t c + t m ) t=Ht_c+(1-H)(t_c+t_m) t=Htc+(1−H)(tc+tm)

- 同时访问Cache和主存,若Cache命中则停止访问主存

- Cache-主存系统的平均访问时间为 t = H t c + ( 1 − H ) t m t=Ht_c+(1-H)t_m t=Htc+(1−H)tm

- 先访问Cache,发现未命中再访问主存

- 其他概念

- 主存与Cache之间以“块”为单位进行数据交换

- 主存的“块”又叫“页/页框/页面”;Cache的“块”又叫“行”

- 主存地址可拆分为(主存块号,块内地址)的形式

- 每次被访问的主存块,一定会被立即地调入Cache

3.5.2 Cache和主存的映射方式

区分Cache与主存的数据块的对应关系

- Cache中存储的信息

- 全相联映射——主存块可以放在Cache的任意位置

- 直接映射——主存块只能放在特定的位置:Cache块号=主存块号%Cache总块数

- 组相联映射——主存块存放在特定分组的任意位置:组号=主存块号%Cache分组数

3.5.3 Cache替换算法

解决Cache与主存容量不匹配的问题

- 随机算法(RAND, Random)

- 先进先出算法(FIFO, First In First Out)

- 近期最少使用(LRU, Least Recently Used)

- 最不经常使用(LFU, Least Frequently Used)

3.5.4 Cache写策略(更新策略)

(CPU修改了Cache中的数据副本)确保主存中数据母本的一致性

- 写命中(CPU要写的主存块被命中,已经被调入到Cache中)

- 全写法(写直通法,write-through)

访存次数增加,速度变慢,但更能保证数据一致性- CPU既将数据写入Cache,又要写入主存对应的存储单元中

- Cache块被替换时无需写回

- 写缓冲(write buffer)——减少访存次数(对全写法的优化)

- 组成:由SRAM实现的FIFO队列(先进先出)

- 具体实现:

- 当CPU将某个地址写入Cache且命中,也会同时写入写缓冲中

- 再在专门的控制电路的控制下逐一写回主存(同步到主存中)

- 优缺点:

- CPU写的速度很快,若写操作不频繁,效果很好;

- 写操作很频繁,会因写缓冲饱和(容量有限) 发生阻塞,CPU需要进行阻塞等待

- CPU既将数据写入Cache,又要写入主存对应的存储单元中

- 写回法(write-back)

减少了访存次数,但存在数据不一致的隐患- (CPU只会)向Cache的数据副本中写入相应的数据

- 只有当该Cache块 被替换时,才将整块写回主存

- 未被修改的块 被替换时不写回主存——节省部分写回时间

- 脏位

机器判断该Cache块是否被修改- 1表示被修改,0表示未被修改

- 若该Cache块脏位为1,则根据标记(22位) 写回主存

- 有效位

- 通常搭配脏位一起使用

- (CPU只会)向Cache的数据副本中写入相应的数据

- 全写法(写直通法,write-through)

- 写不命中(…未被命中)

- 写分配法(write-allocate)

- 当CPU对Cache块写不命中,先将要写的地址从主存中调入Cache,再对该Cache块进行写操作

- 主存内容保持不动,CPU只修改(Cache中的)数据副本

- 常搭配写回法

- 非写分配法(not-write-allocate)

- 当CPU对Cache块写不命中,CPU只会对主存进行写操作,而不调入Cache

- 只有读操作未命中时才调入Cache

- 常搭配全写法

- 写分配法(write-allocate)

- 多级Cache

- 多级Cache结构

- ∣ C P U ∣ L 1 C a c h e + W r i t e B u f f e r ( 写缓冲 ) ∣ L 2 C a c h e ∣ D R A M ( 主存 ) ∣ |CPU|L_1\ Cache+Write Buffer(写缓冲)|L_2\ Cache|DRAM(主存)| ∣CPU∣L1 Cache+WriteBuffer(写缓冲)∣L2 Cache∣DRAM(主存)∣

- 离CPU越近速度越快,容量越小

- 各级Cache间常采用“全写法+非写分配法”

- Cache和主存间常采用“写回法+写分配法”

- 多级Cache结构

3.6 虚拟存储系统

两门课这一部分的内容相关性强——对应OS的第三章——虚拟存储器

常作为计组+OS的综合考点

3.6.1 页式存储器

3.6.2 虚拟存储器——计组比较粗略——重点在OS

用户感知到虚拟系统的容量要比它物理上的真实容量要大——OS虚拟性的体现

基于局部性原理

第四章~第七章内容

计算机组成原理 学习笔记II