在 Xilinx Zynq 系列(如 Zynq-7000 或 Zynq UltraScale+)中实现数字相敏检波(DSP,Digital Synchronous Detection)可以通过硬件(PL部分,FPGA逻辑)和软件(PS部分,ARM Cortex-A 处理器)的协同工作来实现。以下是一个详细的设计方法,包括基本原理和 Zynq 的实现步骤。

1. 数字相敏检波的基本原理

数字相敏检波是一种从输入信号中提取特定频率和相位信息的方法,广泛用于锁相环、涡流检测和调制解调器中。

输入信号模型

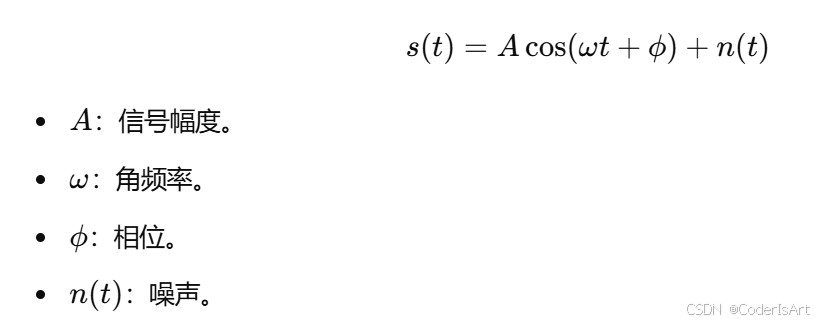

输入信号通常表示为:

数字相敏检波过程

-

正交解调: 将输入信号与本地正弦和余弦信号相乘: