尽管业界尚未达成共识,但“可制造性设计”这一术语大致描述了旨在提高产品良率的特定分析、预防、纠正和验证工作。这不同于后GDSII阶段的分辨率增强技术,如光学邻近效应校正(OPC)和相位移掩膜(PSM)。“可制造性设计”中的关键词是“设计”,意指在设计阶段(而非设计完成后)进行的相关工作。可制造性设计通常与“良率设计”这一术语可以互换使用。

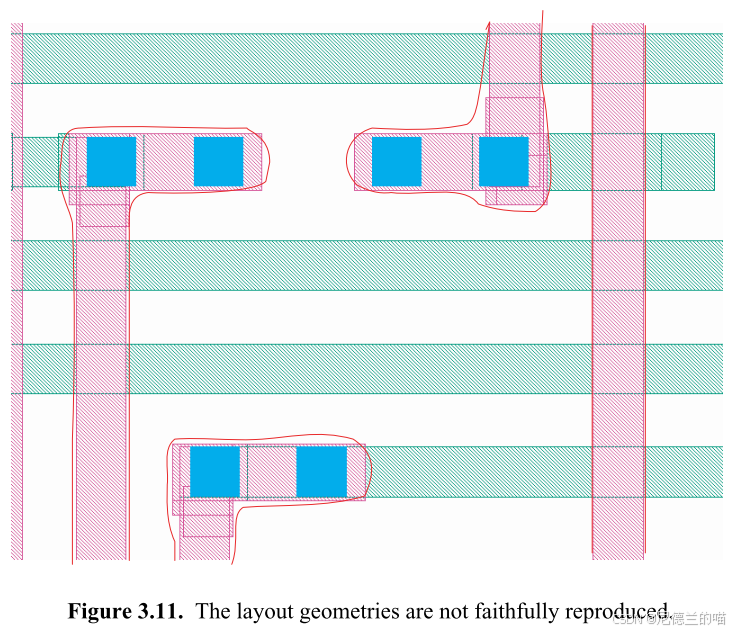

随着工艺技术缩小到0.13微米以下,可制造性设计已成为实现可接受制造良率的严峻挑战。这是因为集成电路的特征尺寸现已小于用于其制造的光的波长。因此,设计阶段生成的布局图形无法被精确复制。这种情况类似于用宽刷子打印细线,图3.11展示了这样的问题之一。在较旧的工艺节点中,例如0.25微米或0.18微米技术,工程师关注诸如金属槽宽度控制、满足密度要求的虚拟金属填充、冗余通孔等问题。这些问题也属于可制造性设计的范畴。

过去,大多数ASIC设计工程师与制造过程相对隔离。设计和制造被视为两个独立的领域,仅通过设计规则和一些推荐规则连接在一起。IC设计师只要严格遵守这些规则&